유튜브에 정리해 놓은게 있는데 아래 글로 보는 것보다 한 10000배는 더 이해 잘 될 것이다. 글은 그냥 회로만 갖다 놨다.

그러니 유튜브로 보는 걸 추천한다. 제발.

먼저, 래치와 플립플롭의 가장 큰 차이점은 무엇일까?? 클럭의 유무로 생각할 수 있지만 클럭이 있는 래치도 있기 때문에 정답이라 할 수 없다. 정답은 시점의 차이다.

래치는 레벨 트리거에서 동작하고 플립플롭은 에지 트리거에서 동작한다.

래치는 지난번에 알아봤고 이번에는 플립플롭에 대해 알아볼 것이다.

2022.01.06 - [내가 하는 전자공학/논리회로] - 논리회로 래치 ( 인버터형 래치, NAND형 SR래치, NOR형 SR래치, RS 래치, D래치 )

논리회로 래치 ( 인버터형 래치, NAND형 SR래치, NOR형 SR래치, RS 래치, D래치 )

래치 (Latch) 래치는 인에이블(허용)이 되면 레벨을 감지하여 입력값을 출력으로 계속해서 전송한다. 클럭 입력을 갖지 않은 쌍안정 회로인데 플립플롭과 유사하나 클럭이 없으므로 비동기식 순

wpaud16.tistory.com

플립플롭에는 여러 종류가 있다. 또 하나의 플립플롭을 설계하는데도 여러 방법이 있다. 가령, 래치 기반, 클럭형, 마스터-슬레이브, NOR 게이트를 사용하느냐, NAND게이트를 사용하느냐, 등등 하지만 실제로 설계할 때는 크게 중요하지 않다.

이번에는 기본적인 특성을 알아보도록 하겠다.

D F/F

마스터-슬레이브 구조로 D 플립플롭을 설명할 것이다. D 플립플롭의 특성표는 위와 같다. 입력과 출력이 동일한 상태로 보면 된다.

위 그림은 D 플립플롭으로 D 래치 2개를 이어 붙인 것이다. (2개 래치 = 플립플롭) 앞단에 있는 D래치를 마스터, 뒷단에 있는 D래치를 슬레이브라고 한다.

천천히 보자,

IN에 1을 입력했다고 해보자

1) CK이 0일 때

- 마스터 부분에서의 출력은 1 그대로 나갈 것이다.

- 슬레이브 부분에서는 입력이 들어오나, CK가 0이라 동작하지 않을 것이다.

2) CK가 1로 올라가는 순간

- 마스터 부분에서는 동작하지 않을 것이다

- 슬레이브 부분에서는 들어오고 있던 입력이 출력으로 나갈 것이다

본인이 이해하기 쉽게 그림으로 보자

A는 CK가 상승 에지일 때는 그전을 유지하다가, 하강 에지일 때 in을 그대로 출력하는 동작을 한다.

OUT은 CK가 상승 에지일 때는 A값을 출력하고 하강 에지일 때는 전 값을 그대로 유지한다.

이렇게 때문에 플립플롭이 에지에서 반응한다고 보는 것이다. 즉, D F/F 의 특징인 상승 에지에 따라 입력값을 그대로 출력시키는 것이다.

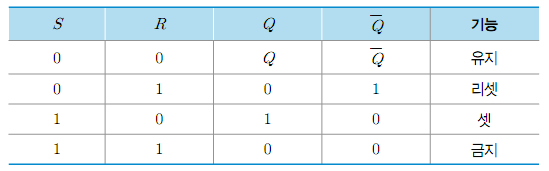

SR F/F

SR F/F은 간단하다. SR 래치에 AND 게이트를 단것이다. 근데 입력이 11 일 때는 사용을 못하는데 이것을 보안하기 위해 나온 것이 JK F/F이다.

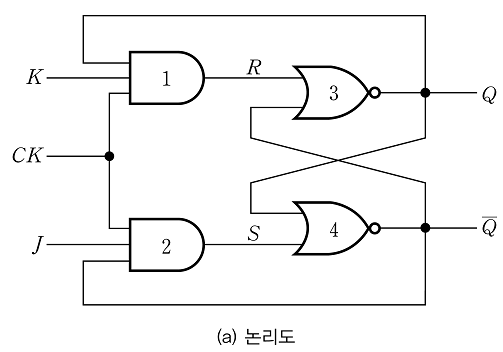

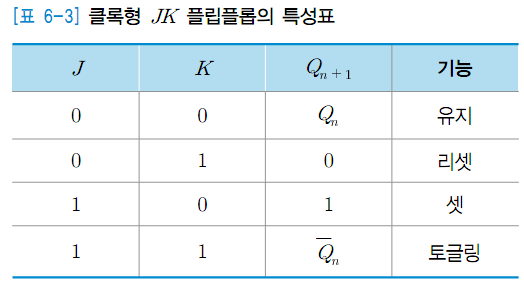

JK F/F

D F/F과 함께 시스템에서 가장 많이 사용한다. J는 S에 대응하고 K는 R에 대응한다. SR에서 사용하지 못했던 11을 토글링함으로 대체한다.

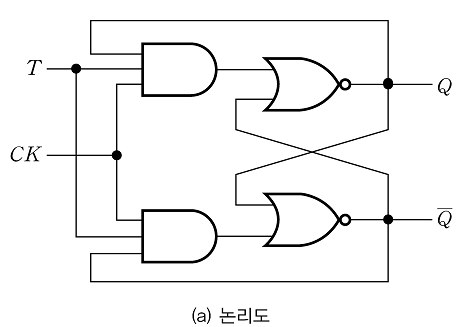

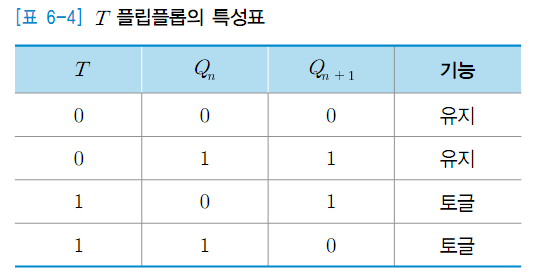

T F/F

JK F/F 에서 JK자리에 하나의 입력을 집어넣는 것이다. T가 0일 때는 이전의 값을 그대로 유지하고 1이 되면 토글. 즉, 값을 뒤집는 것이다.

'반도체 기초 공부 > 논리회로' 카테고리의 다른 글

| 논리회로 프리셋과 클리어 (preset, clear) (0) | 2022.01.11 |

|---|---|

| 논리회로 플립플롭 변환 ( JK F/F을 다른 F/F으로 변환 ) (0) | 2022.01.11 |

| 논리회로 마스터-슬레이브 구조 ( D 래치, 타이밍도, 플립플롭, F/F, 에지 트리거 ) (0) | 2022.01.11 |

| 논리회로 트리거링 기법 ( triggering, 타이밍 파라미터, 레벨트리거, 에지트리거, 숏 펄스 트리거, setup time, holdtime ) (0) | 2022.01.11 |

| 논리회로 무어머신, 밀리머신 개념과 차이 (Moore, Mealy) (2) | 2022.01.06 |

댓글