DRAM Write

DRAM의 Write 동작에 대해 알아보자.

앞선 포스팅에서는 Read / Write을 하기 위한 준비 동작을 작성했다. Refresh, Precharge, Acitve, Read 등등.. 혹시 잘 모르겠다면 아래 링크를 참조하면 도움이 조금은 될 것이다.

2023.04.19 - [내가 하는 공부/DRAM] - DRAM Refresh 동작 ( Self Refresh, 순서, 방식, Charge Sharing )

2023.04.24 - [내가 하는 공부/DRAM] - DRAM Charge Sharing (전하 공유, BLSA, Bit Line Bar)

2023.05.03 - [내가 하는 공부/DRAM] - DRAM PreCharge ( 동작 순서, 이유 )

2023.05.12 - [내가 하는 공부/DRAM] - DRAM Active 동작 (Restore, Precharge, Refresh)

Write의 간단한 동작에 대해 알아보자.

Write는 Read의 반대 동작이라고 생각하면 쉽다. Data가 나가도(Read) Bit Line Sense Amp에는 여전히 Data가 Latch로 유지 돼 있다. 이 유지돼 있는 Data를 다시 Cell에 쓰거나 반대 Data가 들어오면 그 Data를 Cell에 쓰면 된다.

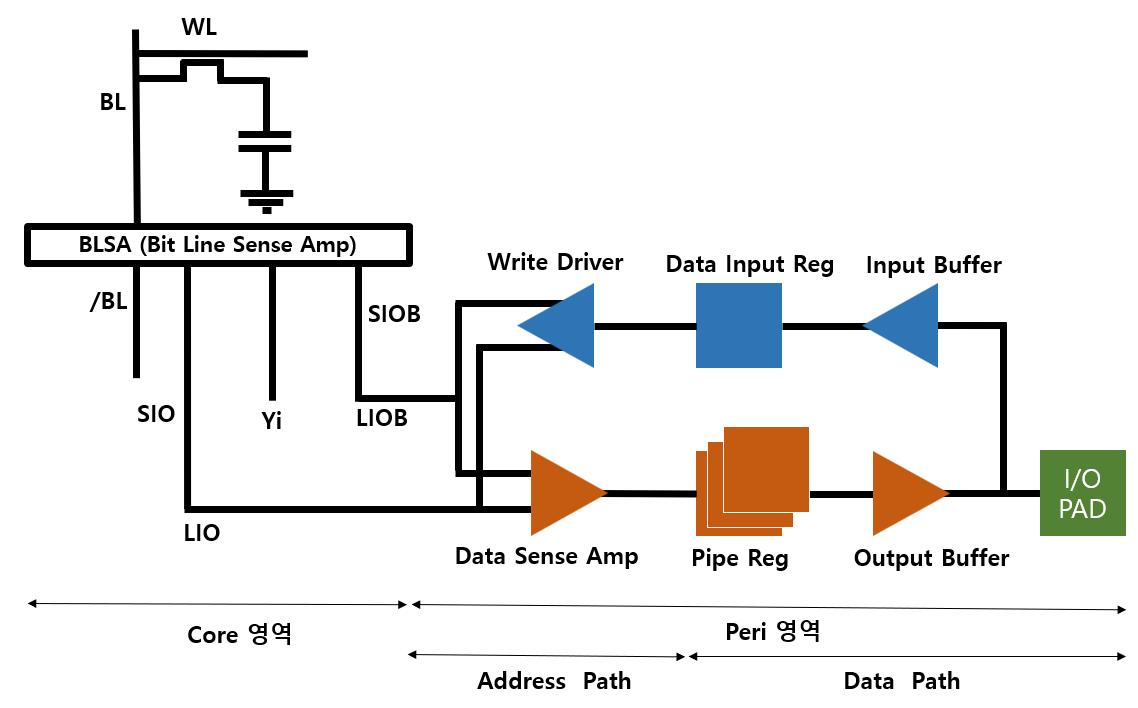

Read / Wrtie 하기 전에는 항상! Active 상태가 돼 있어야 한다는 걸 기억했으면 좋겠다. 그러니 Row가 선택돼 있는 상태인 Active 상태에서 Write Command가 들어오면 위 그림에서 주황색 부분에 해당하는 Read Path는 Disable 된다. 그리고 파란색 부분에 해당하는 Write Path가 활성화된다. DQ(IO) Pad로 들어오는 Data가 파란색 부분을 통해 이동한다.

GIO를 거쳐서 Write Drive가 LIO를 구동한다. 다시 SIO를 거쳐서 Bit Line Sense Amp로 전달되어 기존에 가지고 있던 Data와 싸워서(Fighting) Data가 뒤집힌다. 만약에 기존에 0의 Data를 가지고 있었는데 Write가 1의 Data가 들어온다면, 0을 1로 바꿔준다는 의미다.

뒤집힌 Data가 Bit Line (BL)을 거쳐서 Cell에 Write 하게 된다. 이게 Write Path이다.

'메모리 반도체 > DRAM' 카테고리의 다른 글

| DRAM CBT (Command Bus Training, CBT Sequence, Vref, CA timing, CDC) (1) | 2023.10.21 |

|---|---|

| DRAM ZQ Calibration, ODT (NT-ODT, DDR, ZQ Cal, On Die Termination) (0) | 2023.09.28 |

| DRAM Read 동작 ( Read Path, x8, x16, Burst Length, LSA , IOSA, GIO, LIO, SIO) (0) | 2023.06.10 |

| DRAM Active 동작 (Restore, Precharge, Refresh) (0) | 2023.05.12 |

| DRAM PreCharge ( 동작 순서, 이유 ) (0) | 2023.05.03 |

댓글