DRAM Read

DRAM은 메인 메모리로, Cell에 정보를 가지고 있다가 Command에 따라 Cell 정보를 Read / Write 하는 동작을 반복하는 소자다. 이번 포스팅에는 Read 동작에 대해 알아보자.

앞선 포스팅에서는 Read / Write을 하기 위한 준비 동작을 작성했다. Refresh, Precharge, Acitve와 같은 동작을 말이다. 개념이 헷갈리다면, 아래 링크를 참고하기 바란다.

2023.05.12 - [내가 하는 공부/DRAM] - DRAM Active 동작 (Restore, Precharge, Refresh)

2023.05.03 - [내가 하는 공부/DRAM] - DRAM PreCharge ( 동작 순서, 이유 )

2023.04.19 - [내가 하는 공부/DRAM] - DRAM Refresh 동작 ( Self Refresh, 순서, 방식, Charge Sharing )

2023.04.13 - [내가 하는 공부/DRAM] - DRAM 구조 (LPDDR5, Die, BANK, Core, HEX, MAT)

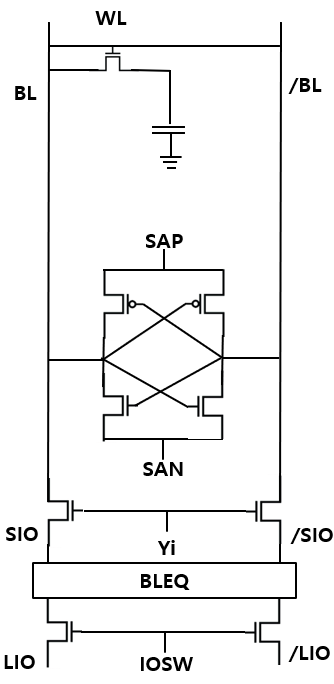

Read / Write 하기 위해선 먼저 Active 동작을 수행해야 한다. 그래야 Restore까지 완료 됐기 때문에 Cell에는 온전한 데이터가 보존 돼 있고, BLSA (Bit Line Sense Amplifier) 에는 증폭된 데이터를 Latch로 보존하고 있다.

실제로 Read는 Cell의 데이터를 읽는 것이 아니라, BLSA에 있는 데이터를 읽는다. 둘은 같은 데이터를 가지고 있는데 Cell까지 가는 것보다 BLSA에 있는 데이터를 읽는 것이 더 효율적이기 때문이다.

Active가 돼 있는 게 기본 Setting이다. 이제 CPU(AP)가 DRAM에 CA (Command / Address) Pin을 통해 정보를 던진다. 이때, Command Pin을 통해 "Read" Command가 들어온다. 그럼 그때 Address Pin으로 들어오는 Address를 해당 Column (X) Address로 Decoding 해서 선택한다. 즉, Yi가 선택한다.

+ Bit Line과 Bit Line Bar의 신호가 60% 벌어지면 Yi를 인식한다.

+ BL, /BL, SIO, /SIO와 같이 Differential Signal (Bar) 신호로 들어가는 이유는 참조 Signal로 이용하기 위해서다.

Row (Y) Address (Word Line)는 왜 선택 안 하냐고 할 수 있는데, Word Line은 Read 하기 전에 이미 Active로 선택했기 때문에 선택할 필요가 없다.

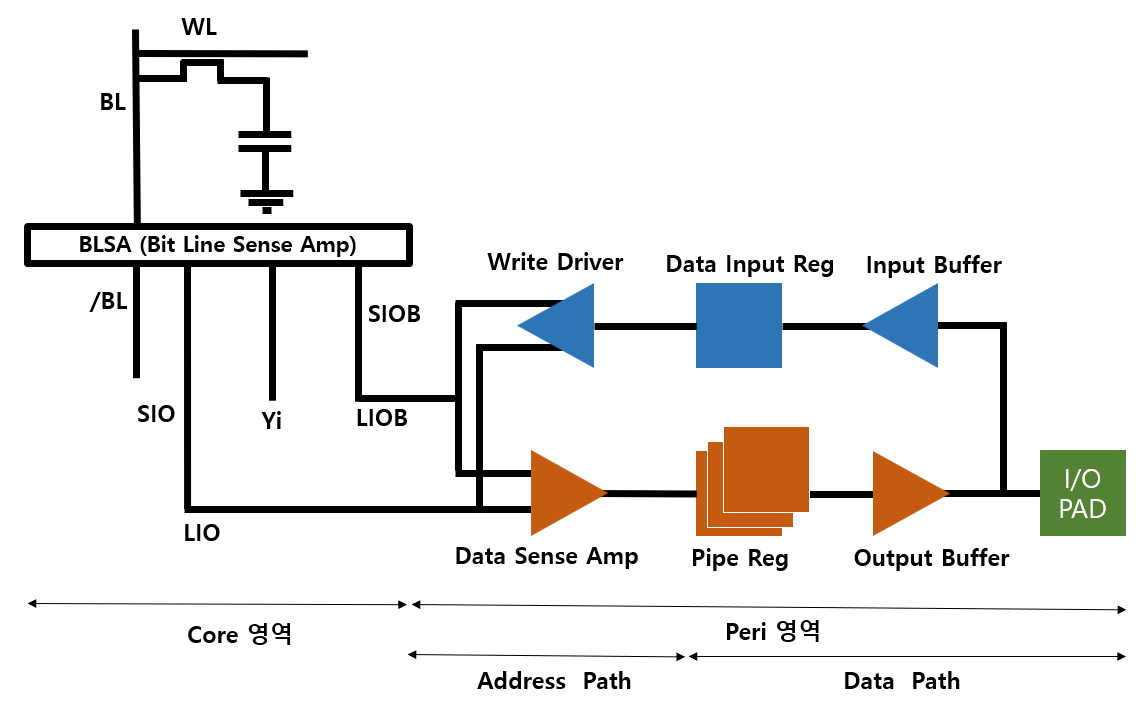

Data의 이동은 자동차의 도로와 비슷하다. 좁은 길에서 점차 넓은 길로 이동하는 것처럼, Bit Line - SIO (Segment IO) - LIO (Local IO) - GIO (Global IO) - IO Pad를 통해 데이터가 이동한다.

위 그림을 보면 BL을 통해서 Bit Line Sense Amp에 Data가 Latch 돼 있다가. Yi가 선택되면 (전압이 인가되면), Latch 돼 있던 Data가 SIO (Segment IO)로 흘러간다. 다음은 *BLEQ (Bit Line Equalization)를 지나 *IOSW (IO Switch)에 전압이 인가되면 SIO에서 LIO (Local IO)로 Data가 이동한다.

*IOSW (IO Switch) : LSA (Local Sensing Amp) 방법을 사용한다. Read 시에만 적용하는데 원래는 단순 IOSW로 SIO를 Sensing 했는데 LSA는 Sensing과 Amp를 해서 LIO에 전달해 준다. 증폭까지 해주기 때문에 IOSA에 들어가는 LIO와 /LIO의 전압 차이가 커서 IOSA의 Start Timing을 앞당길 수 있다.

장점으로는 2nd Read Fail이 사라지는데 이게 뭐냐면, 같은 Address에서 2번 Read 할 때, 첫 번째는 잘 읽고 두 번째는 SIO에서 Bit Line으로 전류가 역류하여 BLSA의 Data가 뒤집히는 현상을 말한다. 단점으로는 더 많은 Transister를 사용하고, Read, Write를 구분하기 위해서 배선이 증가하여 전류 소모가 크다.

근데 LIO까지 오면 Data가 비실비실해져서 정보가 약해져 있다. 그래서 Data를 한 번 더 증폭시켜야 하는데 그 역할을 Data Sense Amp (IOSA)가 해준다. 이 과정 때문에 Read가 Write 보다 느리다.

한 번 더 증폭된 Data는 GIO (Global IO)에 들어간다. 그다음은 Pipe Register에 들어가서 병렬로 들어오던 Data를 직렬로 만들어준다. 그리고 Output Buffer를 통해 I/O Pad로 이동하여 DRAM 밖으로 나간다. 이게 Read Path다. 아래 그림을 보면 조금 더 이해가 쉬울 것이다.

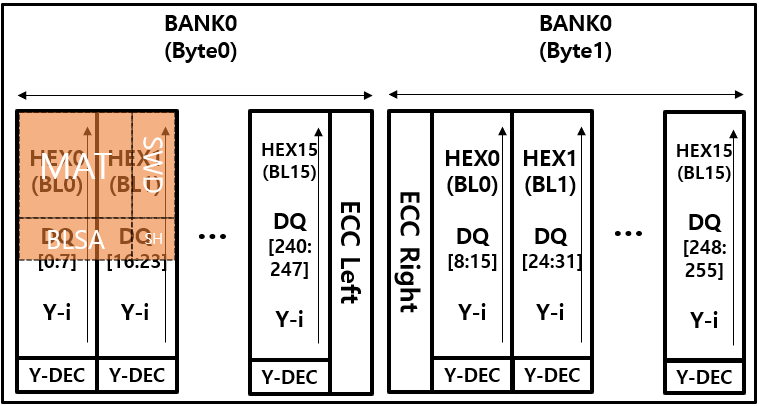

조금 더 자세히 보면, DRAM 구조는 Hex or Octa라는 구조로 나눌 수 있다. 하나의 Bank에 32개의 Hex가 있다고 했을 때, 각각의 Hex에는 64개의 Yi가 있다. 또 하나의 Yi에는 8개의 DQ가 또 달려있다.

그러니 Yi가 선택된다는 건 64개의 Yi 중 하나가 선택된다는 의미고, 각각의 Hex에서 하나의 Yi가 나가니, 8개의 DQ (Cell)이 BL을 통해서 나간다는 의미다.

(1 Bank == 2 Byte == 16*Byte Hex == 64*Hex Yi == Yi*8 DQ)

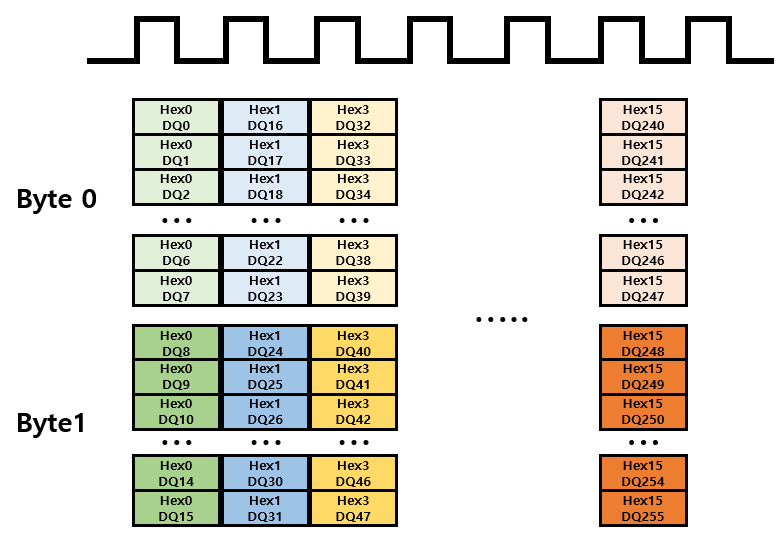

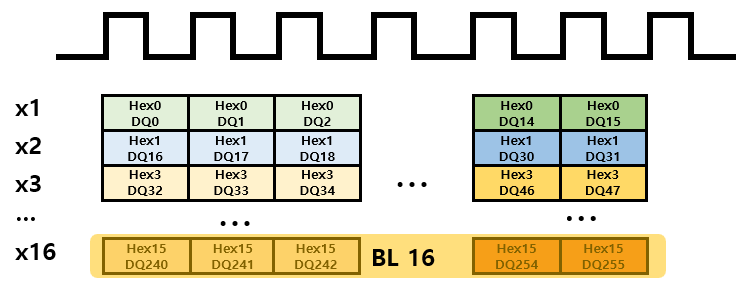

그러면 Byte0과 Byte1의 Hex0에서 각각 8개의 DQ, Hex1에서 각각 8개의 DQ가 클럭에 맞춰서 순차적으로 나간다. 즉, 한 클럭당 16개의 DQ가 나간다. 그러면 Byte 하나에서 128 DQ가 나간다는 의미고, Bank 하나에서는 256 DQ가 Read 한 번에 나가는 것이다. 이렇게 쭉 병렬로 나가다가 Pipe Reg에서 직렬로 변환되어 나간다.

추가적으로 용어를 집어보자. x16, x8이다. by 16, by 8이라고 읽는다.

x16, x8은 서로 다른 자재이다. Data가 나가는 Path의 수이다. 차선으로 생각하면 된다. x16자재는 DQ를 기준으로 보면 Read 한 번에 Data가 16개의 차선을 이용하여 나간다는 의미다.

Burst Length라는 개념이 있는데 이건 Path를 이용하여 나가는 Data의 수이다. 차선을 이용하여 나가는 차의 수라고 볼 수 있다. 한 번의 CLK에 하나의 DQ가 나가는데 나가는 DQ의 수가 16개면 BL16이라고 한다.

x16자재의 BL16이라고 한다면, 1번 Path에는 Byte 0, 1의 Hex0 DQ가 나가고, 2번 Path에는 Hex1의 DQ가 나가고.. 쭉쭉쭉 나간다.

이렇게 Read Path와 Data가 어떻게 나가는지에 대해 알아봤다.

'메모리 반도체 > DRAM' 카테고리의 다른 글

| DRAM ZQ Calibration, ODT (NT-ODT, DDR, ZQ Cal, On Die Termination) (0) | 2023.09.28 |

|---|---|

| DRAM Write 동작 (2) | 2023.08.14 |

| DRAM Active 동작 (Restore, Precharge, Refresh) (0) | 2023.05.12 |

| DRAM PreCharge ( 동작 순서, 이유 ) (0) | 2023.05.03 |

| DRAM Charge Sharing (전하 공유, BLSA, Bit Line Bar) (0) | 2023.04.24 |

댓글