DRAM 구조

메모리의 Spec은 JEDEC이라는 협회에서 합의를 보는데 협의된 Spec에 맞게 제조하면 된다.

근데 DDR5가 LPDDR5 (Low Power)가 있고 GDDR5 (Graphics), 등등 용도에 따라 다르다. 예를 들어 핸드폰에는 LPDDR이 1개 들어가고 컴퓨터에는 DDR이 32개 들어가기도 한다. 하지만 구성과 개요는 유사함으로 LPDDR5를 기준으로 보겠다.

여기서 가정하는 숫자에 연연하면 안 된다. 분야에 따라 너무 다르니 구조에만 신경 써서 보면 좋겠다.

추가적으로 DRAM을 볼 때 8Gb이라고 숫자가 적혀 있는 걸 봤을 거다. Gb는 Giga Bit인데 Die라고 하는 하나의 단위의 Density(용량)를 나타내는 값이다. 예를 들어 아래 그림을 기준으로 8Gb이라고 하면, bit을 Byte로 변경하면 1GB인데, Die가 8개 있으니, 8Gb * 8개 = 8GB (Byte)가 된다.

먼저 DRAM Package(== Chip 1개)를 뜯어보면 Die(다이)라고 부르는 애들이 쫘악 있다. 여기선 Die가 8개 있다고 하자.

+ Channel이라는 개념이 있는데 AP(==CPU)와 Die가 연결 돼 있는 Path를 말한다.

예를 들어 Channel이 4개라고 하면, 아래처럼 A, B, C, D Channel이 독립적으로 움직인다. 같은 Timing에 A에는 Read, C에는 Write 할 수 있다. 또한 Chip Select(CS) Signal로 Die 2개 중에 하나를 선택하여 효율을 높이는 방법을 쓴다.

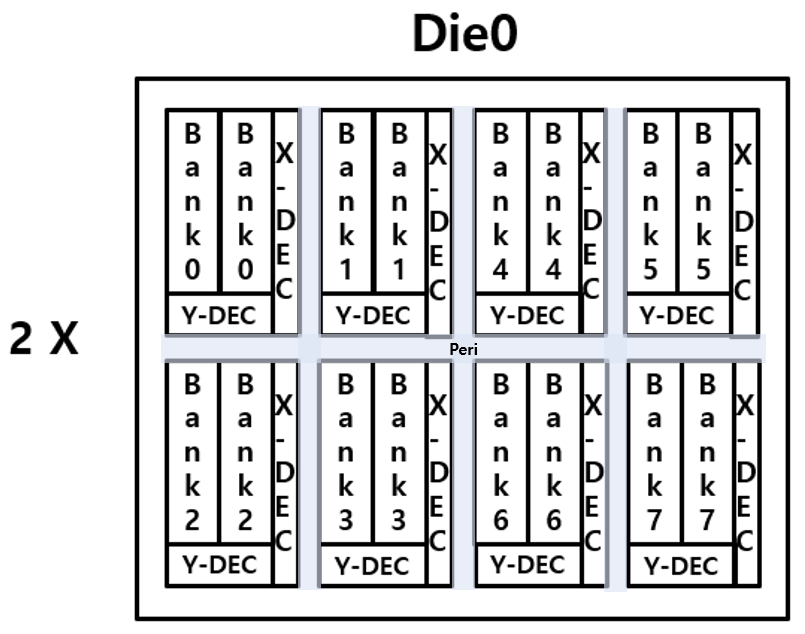

Die는 Bank라는 단위로 쫙 모여있다. 여기서 Bank는 16개라고 가정하자, 컴퓨터에 들어가는 건 32개이기도 하고, Bank의 수는 다 다르다. 다시 말하지만 숫자에 연연하면 안 된다.

각각의 Bank 주변에는 Column(열)을 선택하는 Y-Decoder, Row(행)을 선택하는 X-Decoder가 있다. 또 Bank0를 2개로 나눈 이유는... 정확하게 모르겠다. 지극히 필자의 생각으로는 속도를 높이기 위해서나, Page Size 때문에 저러지 않았을까 싶다. 근데 그냥 Bank 하나라고 이해해도 무방하다.

Bank와 Decoder를 제외한 부분을 Peri (Peripheral)이라고 부른다. DRAM은 CPU와 Command, Address, Data로 총 3개의 독립적인 Path로 연결 돼 있는데 Path를 Control 하는 부분이 Peri 영역이다. 각각의 Path를 조금 보자.

Command는 Active, Read, Write, Precahge와 같은 동작의 명령어를 받는 부분으로 DRAM은 받기만 한다.

Address는 Bank Address나, X-Address (Word, Row), Y-Address (Bit, Col)의 정보를 받는 부분으로 DRAM은 받기만 한다.

Data I/O는 말 그대로 이진수 정보 1 혹은 0을 주고받는 부분으로 양방향으로 Data를 주고받는다. 우리가 64bit, 32bit이라고 하는 건 Data I/O를 기준으로 하는 말이다.

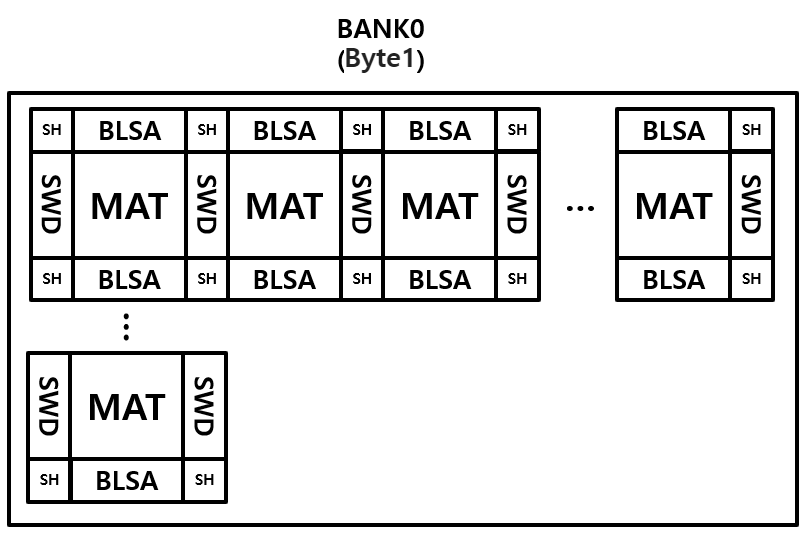

또 하나의 Bank만 확대해서 보자

Core라는 구조의 조합으로 이루어져 있는데 Core는 MAT + BLSA + SWD + SH로 이루어져 있다. 하나씩 간단히 설명하면,

MAT (Matrix)는 메모리 Cell이 모여있는 부분이다. 보통 1K를 기준으로 한다.

BLSA (Bit Line Sense Amplifier)는 Cell에서 나온 값을 증폭시키는 역할을 한다. Read Command가 들어오면 Cell에서 읽는 게 아니라, BLSA에서 증폭된 값을 Read 한다.

SWD (Sub Word Driver)는 Word Line을 선택하는 부분이다.

SH (Sub Hole)은 BLSA를 Control 하는 부분이다.

이렇게 BANK가 이루어져 있다. 아래 그림을 보면 더 이해가 쉬울 것이다.

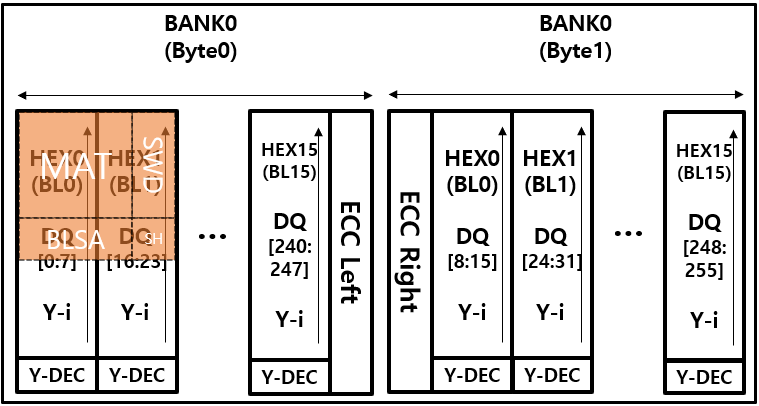

하나의 Bank0는 Byte0, 다른 Bank0는 Byte1으로 불리기도 한다. Bank 내부를 Core 구조가 아닌 Hex라는 개념으로 나눠서 생각할 수 도 있다. 이렇게 나눠서 생각하는 이유는 Data의 Read / Write의 동작을 이해하는데 더 쉽기 때문이다.

16개로 나누면 Hex라고 부르고, 8개로 나누면 Octa라고 부른다. 그냥 Bank를 다르게 나눠서 볼 수 있구나 정도만 이해하면 된다. (+ DDR4는 8개(Octa)로 나눠서 생각하고, DDR5는 16개(Hex)로 나눠서 생각한다.)

간단히 Read / Write시에 어떻게 동작하는지 보면,

하나의 Hex에는 64개의 Yi가 달려있고, Yi 하나에는 8개의 DQ가 달려있다. ( 1HEX = 64Yi, Yi = 8DQ )

DQ가 Bit이라고 생각하면 된다. 숫자는 이해를 돕기 위해 임의로 적었다. DQ는 D Filp Flop을 사용하는 출력 Bit을 말한다.

예를 들어 Read 명령어가 들어오면, Bank0에 X-Dec가 Row를 선택하면 Byte0, 1의 2KB+ECC Cell들이 Active 된다. 다음으로는 Y-Dec를 통해 각각의 Hex에서 1개의 Yi가 선택된다. Yi 1개에는 8개의 DQ가 달려있으니 Hex 하나에서 8DQ가 나온다.

그러면 32개의 HEX가 있으니 * 8을 해주면 256개의 DQ가 Read 된다. 즉, 256Bit(DQ) == 32Byte == 32HEX == 32BL [Burst Length] 이 나온다는 말이다. (+ Burst Length는 데이터를 연속적으로 전송하는 Data의 수를 의미한다.)

Hex를 기준으로 Density를 구하면, 8 * 64 = 512 Cell이고, 16개가 있으니, Bank0 (Byte0) 하나에 8,192개(8Kb)의 Cell이 있다. 그러니 1개의 Mat를 1Kb라고 가정한다면, Byte0에는 총 8개의 Mat가 필요하다고 볼 수 있다.

일단, 구조에 집중해야 하니 여기까지만 하겠다.

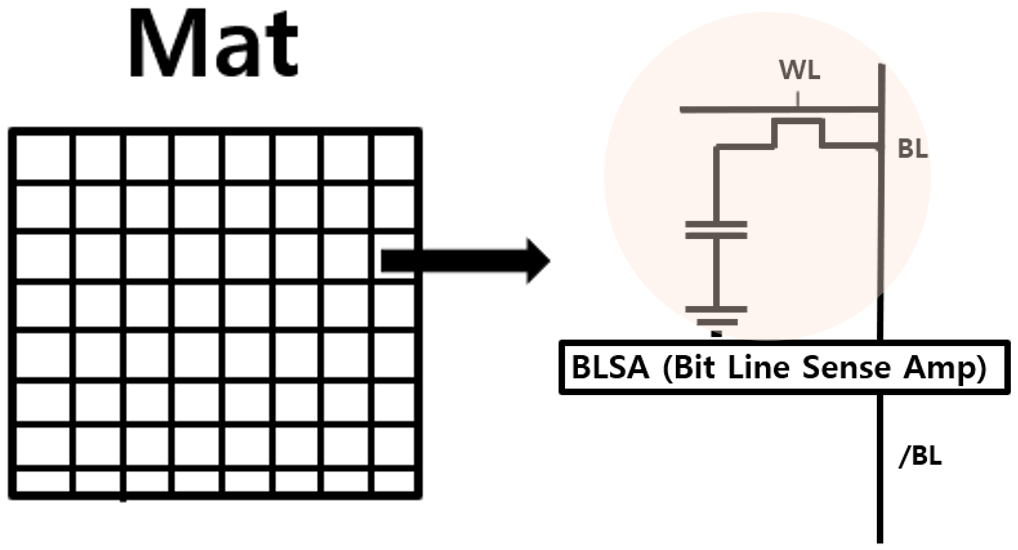

자 이제 얼마 안 남았다. 이제 하나의 HEX의 일부분인 MAT을 확대해 보자.

(+ ECC [Error Correcting Code]라고 해서 Bit Fail을 잡아주는 부분이 있는데 이게 왼쪽 Bank0, 오른쪽 Bank0에 각각 달려있다.)

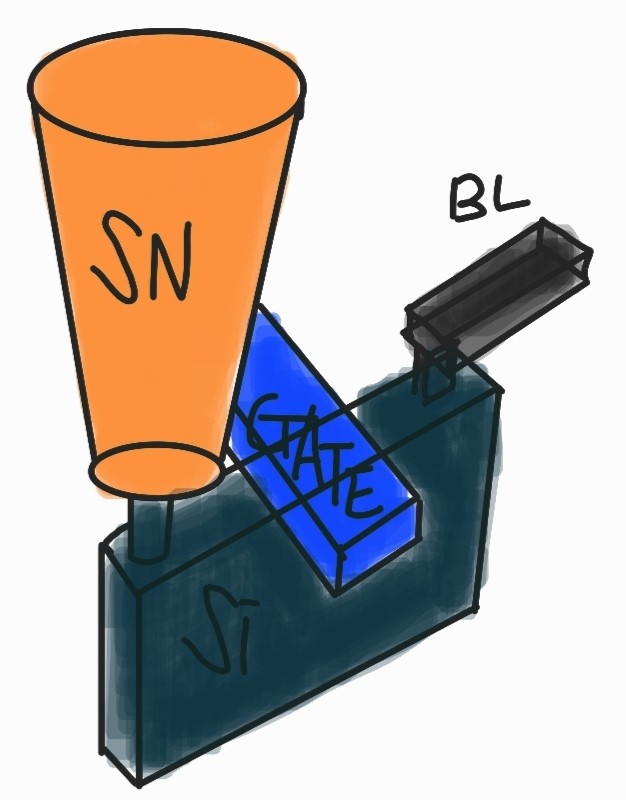

MAT은 Cell이라는 단위로 가로세로 집합이다. 하나를 확대하면 우리가 흔히 아는 WL (Word Line) + BL (Bit Line) + 1-Transister + 1-Capacitor로 하나의 Cell이 구성돼 있다.

전자를 저장하는 Capacitor와 전류의 흐름을 통제하는 Transister와 정해진 Word( == 행, Row)에 전압을 가하는 WL과 정해진 Word의 Capacitor에 있는 전자들이 왔다 갔다 하는 통로인 BL이 있다.

말이 어렵다. 그냥 행렬 구조라고 생각하면 된다. WL은 행, BL은 열, 행렬 들어가는 데이터를 Capacitor, 들어갈지 말지를 결정하는 조건들이 Transister라고 생각해도 괜찮다.

위에 사진을 좀 더 입체적으로 보면 아래 그림과 같이 볼 수 있다. (Aspect Ratio (가로/세로 비율)이 높다.)

SN (Storage Node == Capacitor), Gate (==Transister)는 SN의 전위를 단속한다. 다른 말로 Write 할 거냐, 말 거냐, Read 할 거냐 말 거냐를 결정한다. 실제로 사진을 찍어보면 원통처럼 생겨서 길게 모여있다. 살짝.. 빨대가 모여있는 그런 느낌이다.

이 정도로만 DRAM의 구조에 대해 알아봤다. 일단 구조가 이렇게 됐구나 정도로만 이해하면 좋겠다.

'메모리 반도체 > DRAM' 카테고리의 다른 글

| DRAM PreCharge ( 동작 순서, 이유 ) (0) | 2023.05.03 |

|---|---|

| DRAM Charge Sharing (전하 공유, BLSA, Bit Line Bar) (1) | 2023.04.24 |

| DRAM Refresh 동작 ( Self Refresh, 순서, 방식, Charge Sharing ) (2) | 2023.04.19 |

| DRAM Leakage (Off Leakage, Junction Leakage, DRAM 누설전류, Delpetion) (0) | 2023.04.18 |

| Memory 반도체란 (ROM, RAM, 차이점, 종류) (0) | 2023.03.27 |

댓글