DRAM Charge Sharing

별거 없다. 번역 그대로 전하를 공유하는 것이다.

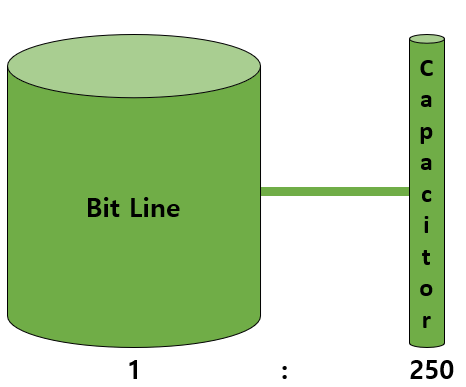

누구랑 공유하냐, Cell Capacitor와 Bit Line Capacitor를 전자가 공유한다. 근데 두 Capacitor에는 용량의 차이가 있다. Cell에 있는 Capacitor의 용량과 Bit Line Capacitor를 1 : 1로 매핑하면 250 : 1 정도로 차이가 있다.

하지만 보통 Bit Line 하나에 걸린 Cell Cap이 1024개 정도 되니, Cell Capacitor와 Bit Line Capacitor의 용량은 4 : 1 정도의 비율이 된다.

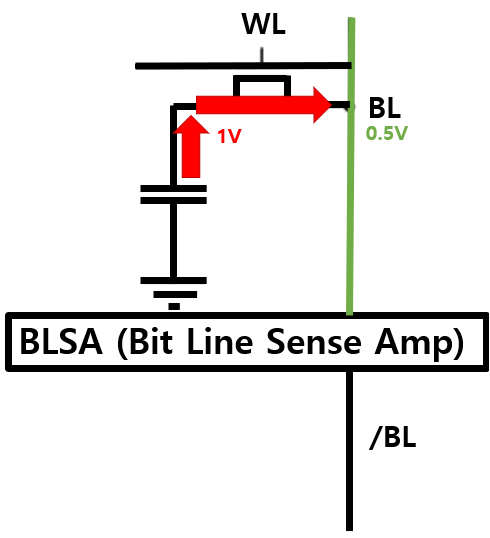

이런 상황에서, Cell Capacitor이 꽉 차 있는 상태에서 상대적으로 조금만 차 있는 Bit Line과 연결된다면 Charging Sharing이 발생한다. 조금 더 쉽게 말하면, 고기압에서 저기압으로, 열평형, 높은 곳에서 낮은 곳으로와 같은 개념으로 이해할 수 있다. 1V로 꽉 차 있는 Cell Capacitor랑 0.5V만 차 있는 BL이 연결되면, 전하가 평행을 이루기 위해 이동한다는 말이다.

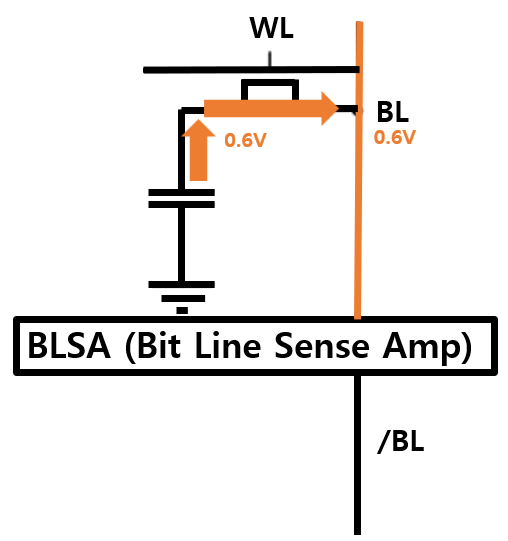

위에서 말했다시피 Capacitor보다 Bit Line이 더 큰 용량을 품을 수 있다. 그러니 Cell Capacitor는 1V에서 0.6V 정도로, Bit Line Capacitor는 0.5V에서 0.6V 정도로 전하가 증가하여 Cell Capacitor와 전압이 맞춰진다.

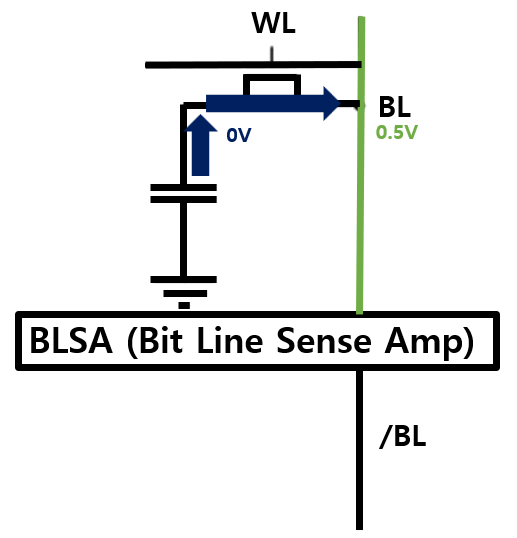

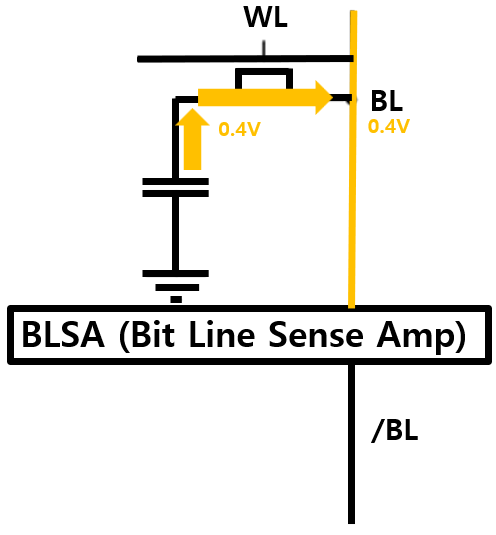

반대로 Cell Capacitor에 0V이 차 있었다면, 0V에서 0.4V 정도로, Bit Line은 0.5V에서 0.4V 정도로 전하가 맞춰진다.

이게 Charging Sharing이다.

여기서 중요한 건 /BL (Bit Line Bar)는 항상 0.5V인 상태라는 점이다.

같은 Bank 내에서는 하나의 Row만 Active 할 수 있다. 이 때문에 Row에 걸린 Bit Line만 0.5V에서 0.6V 혹은 0.4V로 Charge Sharing이 일어난다. 다른 Bit Line은 0.5V로 돼 있다가 Bit Line Sense Amp에서 Charge Sharing 된 Bit Line과 비교한다.

이 과정에서 Bit Line에 걸린 전압을 0.6V는 1V로, 0.4V는 0V로 된다. /BL가 0.5V이기 때문에 이 전압보다 크면 1V, 작으면 0V로 만들어주는 게 BLSA의 역할이기 때문이다.

Charge Sharing은 간단하게 평형 상태를 맞추고 CPU(AP)가 DRAM의 값을 더욱 정확하게 Read / Write 할 수 있게 하는 과정이라고 생각하면 좋을 것 같다.

'메모리 반도체 > DRAM' 카테고리의 다른 글

| DRAM Active 동작 (Restore, Precharge, Refresh) (0) | 2023.05.12 |

|---|---|

| DRAM PreCharge ( 동작 순서, 이유 ) (0) | 2023.05.03 |

| DRAM Refresh 동작 ( Self Refresh, 순서, 방식, Charge Sharing ) (2) | 2023.04.19 |

| DRAM Leakage (Off Leakage, Junction Leakage, DRAM 누설전류, Delpetion) (0) | 2023.04.18 |

| 메모리 반도체 DRAM 구조 (LPDDR, Die, BANK, Core, HEX, MAT) (3) | 2023.04.13 |

댓글