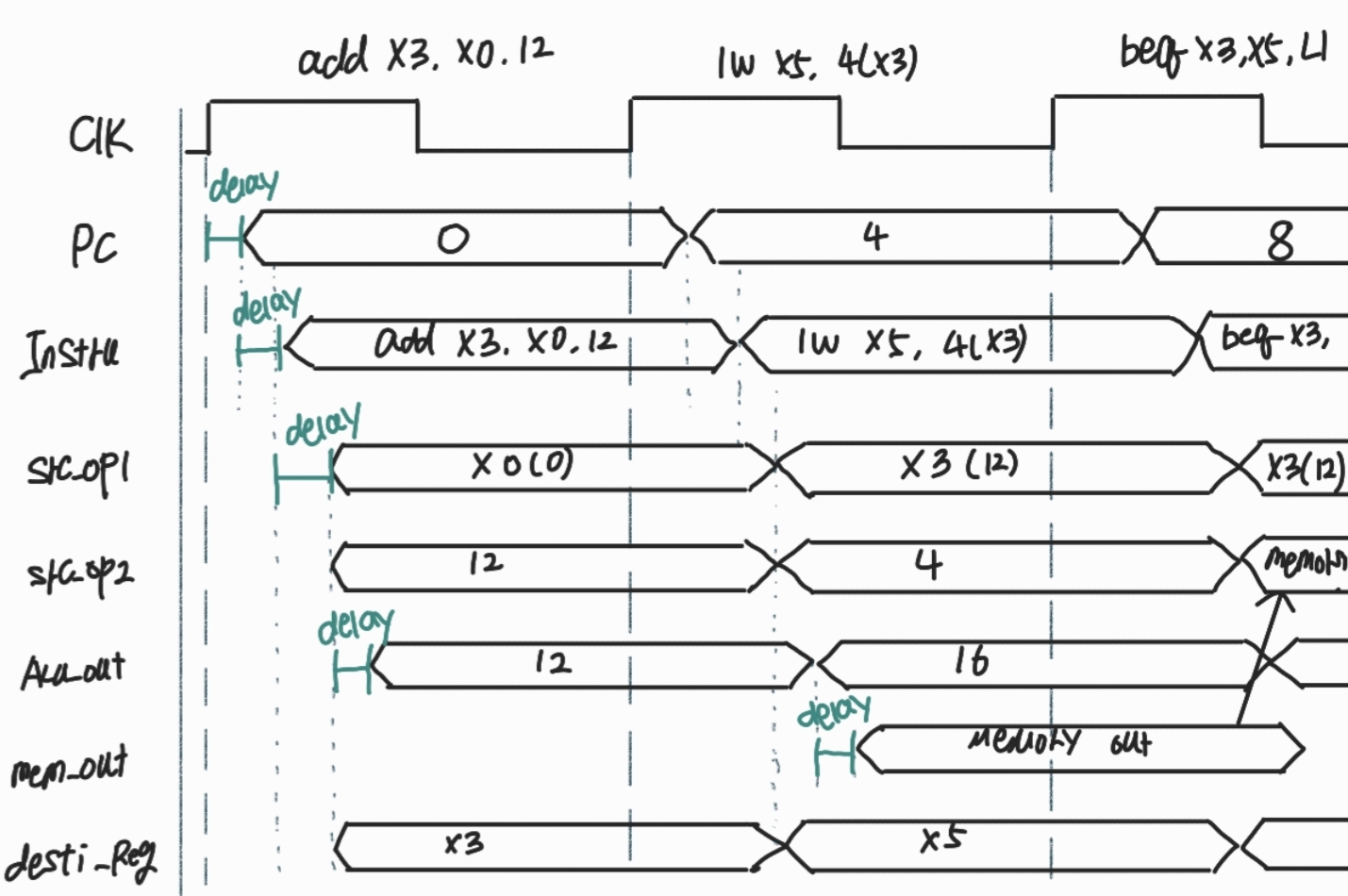

아래의 single cycle에서 wave form이 어떻게 나오는지 보자.

single cycle은 한 번의 클럭에 하나의 명령어를 수행하는 것이다. 그래서 addi, lw, beq명령어를 수행한다고 가정하자.

addi x3, x0, 12

lw x5, 4(x3)

beq x3, x5, L1

첫 번째 클럭이 튀면, addi에서 PC는 F/F delay 후 0으로 세팅된다.

그리고 메모리에서 명령어를 불러온다. 이때도 delay가 생긴다.

그다음에 source 레지스터를 추출하거나 sing extension 하고 목적지 레지스터를 세팅한다. 이때도 delay가 생긴다.

그다음엔 ALU를 이용하여 연산하는데 역시 delay가 생긴다. 그리고 다음 클럭이 튈 때, 연산 값이 x3에 저장된다.

뒤에 동작도 비슷하지만 lw 연산에서 mem_out을 보면, 4 + x3 한 값은 주소 값이다. 이때 그 주소의 값을 뽑아내는데 memory delay가 생긴다. 그리고 뽑아온 값이 beq의 두 번째 sorce로 들어간다. 이유는 lw x5, 4(x3) beq x3, x5 L1을 했기 때문이다.

delay를 위에서부터 정리하면

PC delay : F/F delay

Instrustion delay : 메모리 access delay

Source operand & Destination reg : 레지스터 delay or sing extension delay

ALU out : ALU 연산 delay

Memory out : 메모리 access delay

이렇게 정리할 수 있다.

critical path

위에서 wave를 봤다. 처음 봤을 땐, 이렇게 생각했다. 저렇게 많은 delay가 있는데 만약에서 delay가 쌓여 한 클럭을 넘는다면?? 어떻게 될까?라는 생각을 했다. 하지만 critical path를 알고 나서 궁금증이 사라졌다. critical path는 뭘까?

critical path는 명령어 중에 동작 시간이 가장 오래 걸리는 시간을 말한다. 가령 add, beq, lw 이 셋 중에 명령어 동작이 가장 오래 걸리는 명령어는 무엇일까??

lw이다 일단, 셋 다 pc에서 출발하는 건 동일하다. 하지만 lw는 주소를 계산하고 메모리에 접근도 하고 레지스터에 다시 store 한다. 이런 이유 때문에 가장 오래 걸린다. 이렇게 모호하게 말하니 잘 와닿지 않는다. 그래서 수식이 존재한다.

수식을 말로 풀어쓰면,

최소한의 클럭 주기 == (PC F/F delay) + (instruction memory access delay) + max(register read or sing extension) + (MUX delay) + (ALU delay) + (data memory access delay) + (MUX delay) + (register set up)

이렇게 해서 critical path를 정한다. 근데 마지막에 set up이란 뭘까?? 바로 클럭이 오르기 전과 후 움직이면 정확한 값이 들어가지 않을 수 있어 대기해야 하는 시간이다. 예시로 사진을 찍기 전에 움직이지 않는 것과 비슷하다.

만약 최소한의 클럭 주기가 950ps인데 클럭은 800ps로 하면 어떻게 될까?

클럭 주기가 위의 계산보다 작으면 garbage가 메모리로 쌓인다. 즉, 타이밍이 안 맞는다는 소리다. 그럼 클럭 주기가 넘긴 건 괜찮을까?? 괜찮다. 미리 대기 중이기 때문이다.

950ps라면 주기는 1/T, 1/950ps이다 계산하면 f = 1.052 GHz가 된다.

댓글