마이크로 아키텍처 ISA에는 3가지 정도의 동작 방법이 있다.

1. Single cycle : 한 번의 클럭에 하나의 명령어를 실행한다.

2. Multi- cycle

3. Pipeline : 모든 명령어의 과정을 병렬적으로 실행한다.

이번에는 single과 Pipeline을 알아볼까 한다. 들어가기 전에 어떻게 컴퓨터의 성능을 평가할 수 있을까?

1. Respone time, 각각의 Task가 시작에서부터 끝나는 시간을 평가한다

2. Throughput (슈퍼컴퓨터) 시간 안에 얼마나 많은 양을 처리할 수 있는지를 평가한다

예를 들어보자,

single cycle

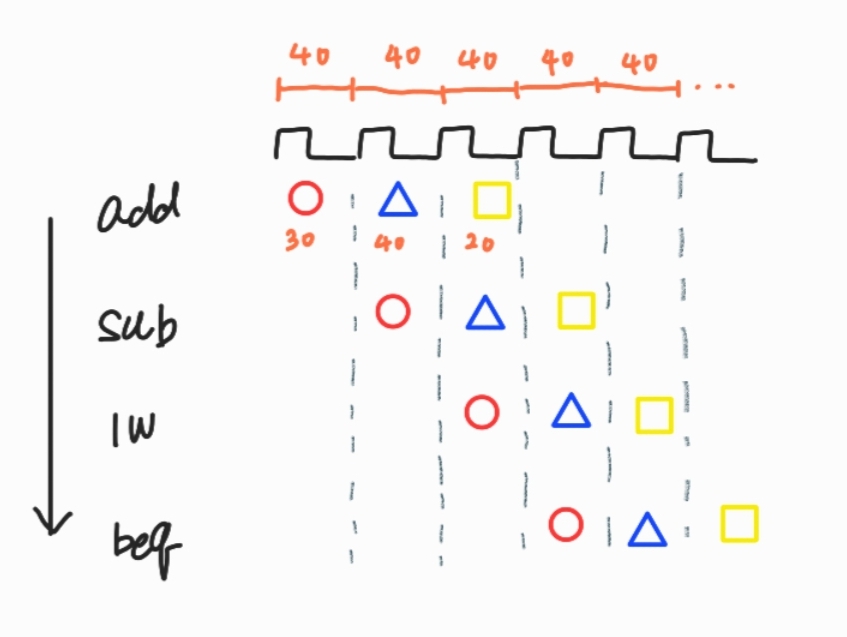

위 그림은 하나의 명령어가 동작하는 시간과 순서를 나타냈다.

동그라미는 30분

세모는 40분

네모는 20분 걸린다고 하면 하나의 동작이 끝나는 데 걸리는 시간은 총 90분이다.

Respone time은 얼마일까? 하나의 명령어가 시작하여 끝나는 데까지 걸린 시간이므로 90분이다.

Throughtput은 얼마일까? 하나의 명령어를 90분 동안 진행하니, 90 min / 1 task이다. 그러니 0.67 tasks/hr라는 값이 나온다.

Pipeline

Respone time은 얼마일까? 하나의 명령어가 시작하여 끝나는 데까지 걸린 시간이므로 여전히 90분이다.

하지만 Throughtput은 얼마일까? 200분 동안 4개의 명령어를 수행했으니 하나의 명령어를 처리하는데 52.5분이 소요된다. 따라서 시간으로 변환하면 1.14 tasks/hr가 된다. 여기서 single cycle과 차이가 난다.

이게 의미하는 바가 무엇일까??

1. 파이프라인은 single task에 있어서 응답 시간은 single cycle과 차이가 없다.

2. 파이프라인은 Throughtput에 도움이 된다

3. 파이프라인은 Multiple tasks를 동시에 실행할 수 있다

4. 파이프라인은 동작당 균일하지 않은 시간에 대해서는 속도를 높이기 어렵다.

- 이 말이 무슨 말이냐면, 동그라미, 세모, 네모가 동작하는 시간이 다른데, 결국 한 사이클에 동작하는 시간은 가장 마지막에 끝나는(긴) 40분으로 맞춰진다는 의미다.

5. Potential speedup은 하나의 명령어가 동작하는 stage의 수이다.

- 좀 더 보자, single cycle이 하나의 명령어를 수행하는 데 걸리는 시간과 비교하면 single cycle은 90분이 걸리고 파이프라인에서, 만약 동그라미, 세모, 네모의 동작이 30분으로 균일하다고 하자.

그러면 90 대 30이므로 Potential speedup은 3x가 된다. 즉, single cycle에서 하나의 클럭이 동작할 때, 파이프라인에서는 몇 번 동작하냐로 볼 수 있다.

균일하지 않다면 제일 긴 시간을 기준으로 한다.

파이프라인의 stage에 관해서 차이점이 궁금하다면 아래 포스팅을 참고하면 이해가 쉬울 것이다.

컴퓨터 구조 Pipelining hazards ( Structure hazards, Data hazard, Control hazard, Critical path, pipeline, 파이프라인,

single cycle은 딜레이가 길다. 그래서 산업에서는 쓰지 않는다. 그렇다면 어떻게 더 나은 결과를 도출할 수 있을까?? 2가지 정도 생각할 수 있다. 1. 반도체 기술이 발전하는 것이다. 트랜지스터의

wpaud16.tistory.com

CPU 동작

조금 자세히 말하자면, 5 stage cpu의 동작 순서는 5단계로 볼 수 있다.

1. Fetch

- PC (Program Counter)가 가리키는 메모리의 주소에 접근하여 해당 명령어의 Machine Code를 CPU Register로 읽어오는 동작이다.

2. Decoding

- CPU Register로 가져온 Machine Code의 Opcode와 Function 정보를 이용하여 어떤 명령어인지 확인하는 동작으로 operands 레지스터 번호 혹은 imm을 가져온다.

3. Excution

- 알아낸 동작에 맞게 ALU을 이용하여 연산을 수행하는 동작이다.

4. Memory

- 메모리에 접근하여 Load/Store를 하는 동작이다.

'시스템 반도체 > 컴퓨터 구조 (RISC-V)' 카테고리의 다른 글

| 컴퓨터 구조 single cycle cpu, critical path (0) | 2022.03.09 |

|---|---|

| 컴퓨터 구조 cpu 동작 ( Fetch, Decodeing, Excution, Data processing, Memory Access, Branch, cpu 동작 순서 ) (0) | 2022.03.08 |

| 컴퓨터 구조 slt, sltu, slti, sltiu, Endianness (RISC-V) (0) | 2022.03.02 |

| 컴퓨터 구조 Branch instruction ( beq, jal, jump 범위, RISC-V ) (0) | 2022.03.01 |

| 컴퓨터 구조 pseudo instructions ( lui, auipc, 가짜 명령어, 의사 코드, RISC-V ) (0) | 2022.02.27 |

댓글