Arm Logical Instruction ( 논리 명령어, AND, ORR, EOR, BIC )

Data processing 중에 Logical instruction을 알아보자 Logical 1. AND - 말 그대로 AND 연산을 시키는데 bit by bit을 시키는 것이다. 단순히 AND R0, R0, #3이라고 하면 3은 마지막만 11이고 나머지는 다 0이니 11과 R0의 마지막 xx와 and 연산을 시켜서 R0에 넣어주면 된다. 2. ORR - AND와 똑같이 bit 연산을 시키는 or 연산자이다. 3. EOR - XOR과 똑같다. eor r0, r0, r0라고 한다면 어떻게 될까? xor은 1이 짝수면 0이고 홀수면 1이다. 조금 다르게 보면 00, 11일 때는 0이고 나머지는 1이다. 이럴 때, 같은 operand라면 결국 둘 다 똑같기 때문에 0으로 초기화되는 효과가 있다. 만약 eor..

2022. 4. 7.

Arm register 종류 ( SP, LR, PC, NZCV, CPSR, APSR, CPS 명령어)

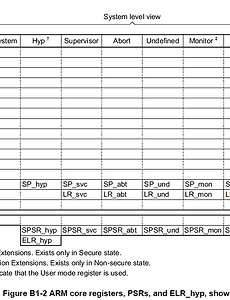

Arm CPU는 16개의 레지스터를 가지고 있으며 서로 다른 9개의 동작을 할 수 있다. System level view에 해당한다. 먼저, 아래 표에서 헷갈리는 용어를 간단히 보자, IRQ는 Interrupt이다. FIQ는 Fast Interrupt Mode이다. R13 == SP ( Stack Pointer ) R14 == LR ( Link Register ) R15 == PC ( Program Counter ) APSR, CPSR는 아래 따로 정리하겠다. 빈칸은 해당 동작을 하지 않아서가 아니라, 어떤 모드일 때든 똑같은 물리적인 주소를 사용하기 때문에 비워놓은 것이다. 무슨 말이냐면, R0 ~ R7까지는 어떤 모드에서 동작을 하더라도 똑같은 자리에서 데이터를 찾는다. 하지만 R8 ~R12는 FIQ..

2022. 4. 7.

Arm register 종류 ( SP, LR, PC, NZCV, CPSR, APSR, CPS 명령어)

Arm CPU는 16개의 레지스터를 가지고 있으며 서로 다른 9개의 동작을 할 수 있다. System level view에 해당한다. 먼저, 아래 표에서 헷갈리는 용어를 간단히 보자, IRQ는 Interrupt이다. FIQ는 Fast Interrupt Mode이다. R13 == SP ( Stack Pointer ) R14 == LR ( Link Register ) R15 == PC ( Program Counter ) APSR, CPSR는 아래 따로 정리하겠다. 빈칸은 해당 동작을 하지 않아서가 아니라, 어떤 모드일 때든 똑같은 물리적인 주소를 사용하기 때문에 비워놓은 것이다. 무슨 말이냐면, R0 ~ R7까지는 어떤 모드에서 동작을 하더라도 똑같은 자리에서 데이터를 찾는다. 하지만 R8 ~R12는 FIQ..

2022. 4. 7.