Arm instruction format (명령어 구조)

Arm은 RISC machine이다. 대부분의 Arm 명령어는 조건에 따라 동작하는데 이건 중요한 특징 중에 하나다. 조건이라 함은, NZCV와 같은 Conditional flags에 해당한다.

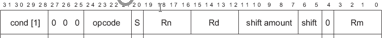

Arm instruction format도 다른 instruction과 유사하게, opcode가 있고, source 레지스터인 Rn, Rm(아래에선 0~11까지)와 destination 레지스터인 Rd가 존재하고 4 bit의 조건 cond bit가 존재한다.

대표적인 instruction format을 가져온 게 아래 그림이다.

(32bit를 기준으로 봤다)

조건에 따른 동작이라 했는데 어떤 경우인지 예를 들어보자,

add 동작을 수행한다 하면, 보통 add x0, x1, x2일 때, x1 + x2를 하여 x1에 넣는다. 하지만 Arm에선 add뒤에 조건이 붙는다. addeq x0 , x1, x2, addne x0, x1, x2와 같이 말이다. 이런 경우에는 eq, ne... 이외에 여러 조건이 있는데 각각에 해당하는 조건이 만족할 때만 add를 수행한다는 의미다. cond flag는 4bit이니 16가지의 경우의 수가 있다. 그러니 opcode가 0000 ~ 1111일 때 동작을 달리한다.

또 다른 예를 들어보자,

if 문을 구현한다면, Arm은 cmp명령어를 통해 뺄셈으로 r2와 r3가 같은지 비교한다.

그리고 같다면, CPSR에 Z flag가 1로 세팅된다. 그리고 addeq (eq = equal) 명령어를 실행한다. 만약 같지 않다면 Z flag가 0으로 세팅되고 subne (ne = not equal) 명령어를 실행한다. 그리고 조건에 맞지 않는 명령어는 nop로 바뀐다. RISC-V는 beq를 통해 jump를 통해 이동했던 것과 다르다는 차이점이 있다.

비교에는 signed, unsigned에 따라 달리하는데 ==, !=는 부호와 상관없이 이루어지기 때문에 동일하고, >, <, >=, <=는 부호에 따라 다르게 이루어진다. 그래서 비교의 조건에는 총 10개의 조건이 있다. 아래 초록색으로 돼 있는 부분이다.

Arm cpu를 간단히 보면 아래와 같다. first source operand는 그냥 바로 ALU로 들어간다. 하지만 second source operand-는 Shifter를 거쳐서 전처리를 하고 ALU에 들어간다. 왜 그럴까?? shifter를 이용하여 내가 원하는 데이터를 가공할 수 있기 때문이다.

예를 들어보자, add r3, r4, r5, lsl #2 명령을 수행한다고 하자. 아직 배우진 않았지만 전체적인 흐름을 보자.

r5를 왼쪽으로 2만큼 shift 시키고, r4와 더해서 r3로 들어간다. 즉 여기선 second source는 r5 lsl #2까지이다.

수식으로 표현하면 r3 = r4 + (r5 << 2)와 같이 표현할 수 있다.

또한 숫자만 해당하는 것이 아니라, 레지스터를 넣을 수도 있다. add r3, r4, r5, lsl r10과 같이 말이다.

'시스템 반도체 > Arm' 카테고리의 다른 글

| Arm Aruthmetic instruction ( 산술 명령어, ADD, ADC, SUB, SBC, RSB, RSC, CLZ ) (0) | 2022.04.07 |

|---|---|

| Arm Move instruction ( 이동 명령어, MOV, MVN, MOVS ) (0) | 2022.04.07 |

| Arm Logical Instruction ( 논리 명령어, AND, ORR, EOR, BIC ) (0) | 2022.04.07 |

| Arm Comparison instruction ( 비교 명령어, CMP, CMN, TEQ, TST ) (0) | 2022.04.07 |

| Arm register 종류 ( SP, LR, PC, NZCV, CPSR, APSR, CPS 명령어) (0) | 2022.04.07 |

댓글