Data processing 중 하나인 Aruthmetic instruction을 알아보자.

Aruthmetic

1. ADD

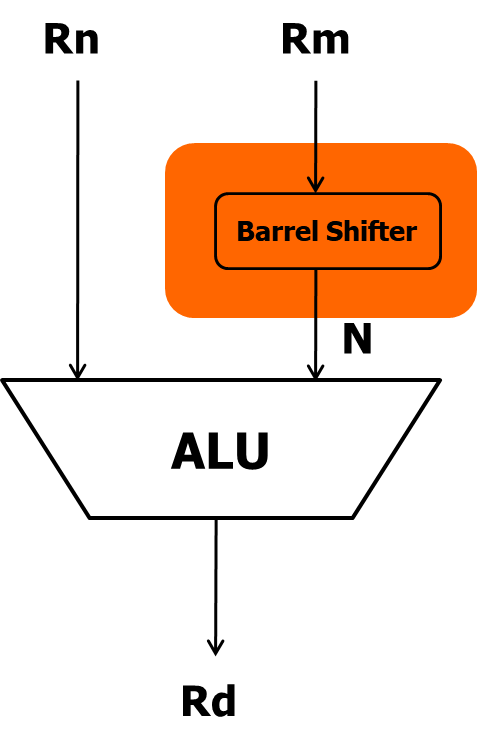

- Rd = Rn + N

굉장히 단순하다. adds는 연산이 끝난 후에 nzcv flag를 업데이트한다는 차이가 있다.

add r0, r1, r2 ; r0 = r1 +r2

add r0, r1, #256 ; r0 = r1 + 256

adds r0, r2, r3, lsl#1 ; r0 = r2 + (r3 <<1)

2. ADC

- Rd = Rn + N + carry flag

32bit Arm cpu에서 64bit을 더할 수 있을까??

가령 c 코드에서 long long a, b, c라고 하고 a = b + c라면 a, b, c 각각이 이미 64bit인데 어떻게 더할 수 있을까?

이때 필요한 게 ADC이다. 아래서 보면, 뒤에 32bit를 먼저 계산하는데 이때 carry를 업데이트해야 하니, ADDS를 이용하고, 다음 앞쪽에서 더할 때는 업데이트된 carry를 반영해야 하니 이때 ADCS를 이용한다. (S를 붙이면 NZCV flag를 업데이트한다)

이렇게 2개의 명령어를 이용해야 64bit를 더할 수 있다.

3. SUB

- Rd = Rn - N

SUB R0, R1, R2 ; R0 = R1 - R2

SUB R0, R1, #256 ; R0 = R1 - 256

SUBS R0, R0, #1

subs r0, r0, #1을 예로 들어보면, r0 = 0x0000_0001이라고 하자 그러면 r0 - 1이다. 즉, 1-1인 것이다.

-1인 + (-1)과 같은데 컴퓨터는 2의 보수를 사용하니 -1을 만들려면 1에서 다 뒤집은 다음에 1을 더해주는 것이다.

1 = 0x0000_0001

~1 = 0xFFFF_FFFE

~1 + 1 = 0xFFFF_FFFE +1 = 0xFFFF_FFFF

0x0000_0001

+0xFFFF_FFFF

=0x0000_0000 + carry

즉 nzcv에서 Z와 C가 1로 세팅되고 r0에는 0으로 업데이트된다.

4. SBC

- Rd = Rn - N - !carry flag

ADC와 마찬가지로 64bit 연산을 할 때 사용한다. 단, 빼기는 항상 2의 보수를 사용한다는 걸 늘 생각해야 한다.

5. RSB

- Rd = N - Rn

Reverse를 의미한다. 이에 RSB r0, r1 #0이라면 r0 = 0x0 - r1이다.

만약 r1 = 0x0000_0077이라면 -r1을 구하려면 2의 보수를 취해야 하니, 모두 뒤집은 다음 1을 더해주면 된다. 다 뒤집으면 0xFFFF_FF88이고 여기에 1을 더하면, 0xFFFF_FF89이고 여기 0을 더하면 되니 r0는 0xFFFF_FF89로 업데이트된다.

6.RSC

- Rd = N -Rn - !carry flag

뒤집고 carry flag를 더해준다.

+ CLZ (count leading zeros)

- 이건 처음으로 1이 나오기 전까지 0이 몇 번 나오자 세주는 명령어다. CLZ R1, R0라고 하고 R0 = 0000_0010_11... 라면 처음으로 1이 나오기까지 0이 6번 나오니 R1에는 6이 들어간다.

'시스템 반도체 > Arm' 카테고리의 다른 글

| Arm Memory Access instruction (메모리 접근 명령어, LDR, SRT, LDM, STM, Stack operation) (0) | 2022.04.07 |

|---|---|

| Arm Branch instruction ( 분기 명령어, B, BL ) (0) | 2022.04.07 |

| Arm Move instruction ( 이동 명령어, MOV, MVN, MOVS ) (0) | 2022.04.07 |

| Arm Logical Instruction ( 논리 명령어, AND, ORR, EOR, BIC ) (0) | 2022.04.07 |

| Arm Comparison instruction ( 비교 명령어, CMP, CMN, TEQ, TST ) (0) | 2022.04.07 |

댓글