module

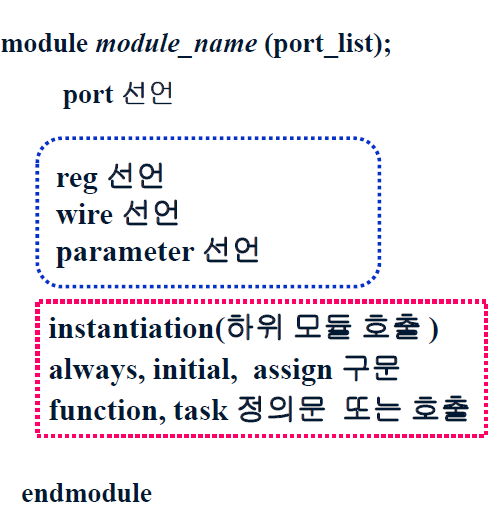

합성을 하기 전에 먼저 module이란 뭔지 알아야 한다. module이란, verilog에서 기본적인 블록 단위로 c언어의 함수와 비슷하다. 아래 그림처럼 도식화할 수 있다.

module_name = module의 이름을 적어준다.

port_list = 입출력을 말한다. 어떤 입출력이 들어가는지 쭉 적으면 된다.

port 선언 = 뭐가 입력, 출력인지 정의한다.

파란색 박스 = 아래 사용할 변수를 선언한다.

빨간색 박스 = 실제로 동작할 코드를 작성한다.

module 연결

아래 그림에서 stage 1과 stage 2 모듈을 만들고 top 모듈을 만들어보자. 즉, stage 1과 stage 2를 연결시켜보자.

stage 1은 입력이 a, b, c, clk 출력이 ff1으로 이루어져 있다. 이루어져 있다. 코드 동작 부분에서 always구문을 썼기 때문에 reg로 선언한다. 또한 and, xor, F/F으로 이루어져 있다.

이를 코드로 나타내면 아래와 같다. 상승 에지일 때 F/F이 동작한다. clk에 버블이 없고 reset동작도 없기 때문이다.

code

module stage1 (a, b, c, clk, ff1);

input a, b, c, clk;

output ff1;

reg ff1;

always @(posedge clk)

ff1 <= (a & b) ^ c;

endmodule

stage 2 입력이 ff1, a, clk, rst 출력이 ff2로 이루어져 있다. 코드 동작 부분에서 stage 1과 마찬가지로 always구문을 썼기 때문에 reg로 선언한다. 소자의 구성은 mux, F/F으로 이루어져 있다.

이를 코드로 나타내면 아래와 같다. 상승 에지일 때 F/F이 동작하지만, 그보다 우선적으로 reset신호에 동작한다. 버블이 있기 때문에 negedge에서 동작한다. clk이 들어와서 reset에 0이 들온 뒤에 동작한다.

code

module stage2 (ff1, a, clk, rst, ff2);

input ff1, a, clk, rst;

output ff2;

reg ff2;

always @(posedge clk or negedge rst) begin

if (!rst) ff2 <= 0

else if (a) ff2 < ff1;

end

endmodule

이제 두 module을 하나의 모듈로 합쳐보자. top모듈을 만들어 두 모듈을 집어넣을 것이다.

top 모듈은 stage 1, stage 2를 불러오는데 인스턴스라는 방법으로 불러온다.

인스턴시란, 모듈을 여러 개 불러올 때, 인스턴시 이름이 따로 존재해야 동일 이름에 대해 혼동을 피할 수 있다. 예를 들어, D F/F 모듈 4개를 불러온다면, 4개 각각에 instance 이름이 있어야 한다. 그래야 동작에 혼란을 주지 않는다.

즉, 새로운 이름을 부여한다는 말이다. 교실에선 모두가 학생이라는 이름을 가지지만, 집에선 각자의 이름으로 불리는 것처럼 말이다.

top module도 module이기 때문에 입력과 출력을 정의한다. 입력으로 t1, t2, t3, clk, res가 있고 출력으로 ff2가 있다.

go는 연결선이라 입력은 아니다.

code

module top(t1, t2, t3, clk, rst, ff2);

input t1, t2, t3, clk, rst;

output ff2;

wire go;

stage1 u1(.a(t1), .b(t2), .c(t3), .clk(clk), .ff1(go));

stage2 u2(.ff1(go), .a(t1), .clk(clk), .rst(rst), .ff2(ff2));

endmodule

생각보다 너무 간단하다. go는 연결이기 때문에 wire로 연결한다.

이제 중요한 stage 모듈을 불러오는 방법이다.

호출하는 방법이 2가지가 있는데 하나는 named mapping이고 다른 하나는 ordered mapping이다.

named mapping (포트 이름에 의한 매핑)

stage 1 u1 (. a(t1),. b(t2),. c(t3),. clk(clk),. ff1(go));

이렇게 불러오는 방법을 named mapping이라고 한다. 이름끼리 연결해주는 것이다. stage 1의 입력과 출력을 top 모듈에서 입출력에 맞게 연결한 것이다.

stage 1의 입력 a를 top에서의 입력 t1에 연결하라는 것이. a(t1)의 의미다.

이렇게 stage 1의 입출력을 모두 연결해주면 top module에서 불러올 수 있다.

추가적으로 u1이 바로 인스턴스 이름이다. stage 1을 top 모듈에선 u1으로 이름을 바꾸겠다는 말이다.

ordered mapping (포트 순서에 의한 매핑)

입력 순서에 대해 1:1로 매핑한 방법이다. 순서가 바뀌 거나하면 안 된다.

module mode ( wa, wb, c, d);

....

endmodule

module top;

...

mode u1( v[0], v[3], w, v[4]);

endmodule

mode 모듈의 입출력이 wa, wb, c, d이다. 이를 top 모듈에서 모을 때, u1이라는 이름으로 불러오는데

mode u1 ( v[0], v[3], w, v[4] );

wa => v[0],

wb => v[3],

c => w,

d => v[4]

이렇게 알맞게 매핑이 된 걸 의미한다. 절대로 순서가 바뀌면 안 된다.

댓글