순차적 논리회로

플립플롭은 대부분 D로 사용한다.

module d_ff (clk, d, q);

input clk;

input d;

input q;

reg q;

always @(posedge clk)

q <= d;

endmodule

clk의 심벌이 상승 에지에서 동작하므로 posedge를 적어준다.

조합 회로와의 always의 차이점은 () 안에 감지 목록이 다르다. 조합회로는 출력에 영향을 주는 모든 입력을 적어주고,

순차 회로는 posedge 또는 negedge 만 사용한다. 이게 차이점이다.

Non-blocking과 blocking

조합 회로와 순차 회로의 또 다른 차이점은 할당문이다. non-blocking과 blocking이 있다.

순차 회로에서는 Non-blocking 할당문을 사용하는데 "<="로 표시한다.

조합 회로에서 blocking 할당문을 사용하는데 "="로 표시한다.

차이점이 뭐냐면 실행의 순서에 차이가 있다. non-blocking는 동시에 실행되는 걸 말하고 blocking은 순차적으로 실행되는 것을 말한다. 조금 다르게 말하면, 병렬적으로 실행되냐 직렬적으로 실행되냐의 차이가 있다.

아래 예를 보며 설정하자면,

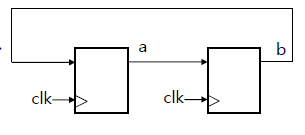

// a = 0; b = 1

// non-blocking

always @(podedge clk) begin

a <= b; // b값을 a로

b <= a; // a값을 b로

end

// blocking

always @(podedge clk) begin

a = b; // b값을 a로

b = a; // 그리고 a값을 b로

end

파형을 보면, non-blocking의 경우 동시에 실행되기 때문에 서로 가지고 있던 값을 교환하는 역할을 한다.

하지만 blocking의 경우에는 순차적으로 실행되기 때문에 첫 번째 코드로 b의 값을 a에 할당하고, a에 값을 b로 할당하니 a, b의 값은 계속 1로 쭉 갈 것이다. 이 말은 값을 저장할 수 없다. 그러니 저장하는 회로인 순차 회로에서 non-blocking을 사용하는 것이다.

+ begin end는 { }의 역할이다

비동기 리셋이 있는 경우

클럭에 상관없이 0일 때 리셋이 된다. 리셋이 가장 우선순위이므로 제일 위에서 판별해야 한다.

reg q;

always @ (posedge clk or negedge rst) begin

if (!rst) q <= 0;

else q <= d;

end

if구문에서! rst은 rst가 0이면 q에 0을 집어넣고

else 구문에서 rst가 0이 아니라면 d값을 집어넣어라는 의미다.

비동기에 리셋과 셋이 있는 경우

rst는 clk에 상관없이 0이면 0으로 되고, set도 클럭에 상관없이 0이면 1이 된다. (그림에 버블이 붙어서)

reg q;

always @ (posedge clk or negedge rst or negedge set) begin

if (!rst) q <= 0;

else if (!set) q <= 1;

else q <= d;

end

always () 안에는 최대 3가지만 넣을 수 있다. 추가적으로 감지 목록에 상승, 하강 에지를 사용하지 않으면 래치가 발생한다.

댓글