기본 파일 생성하는 순서

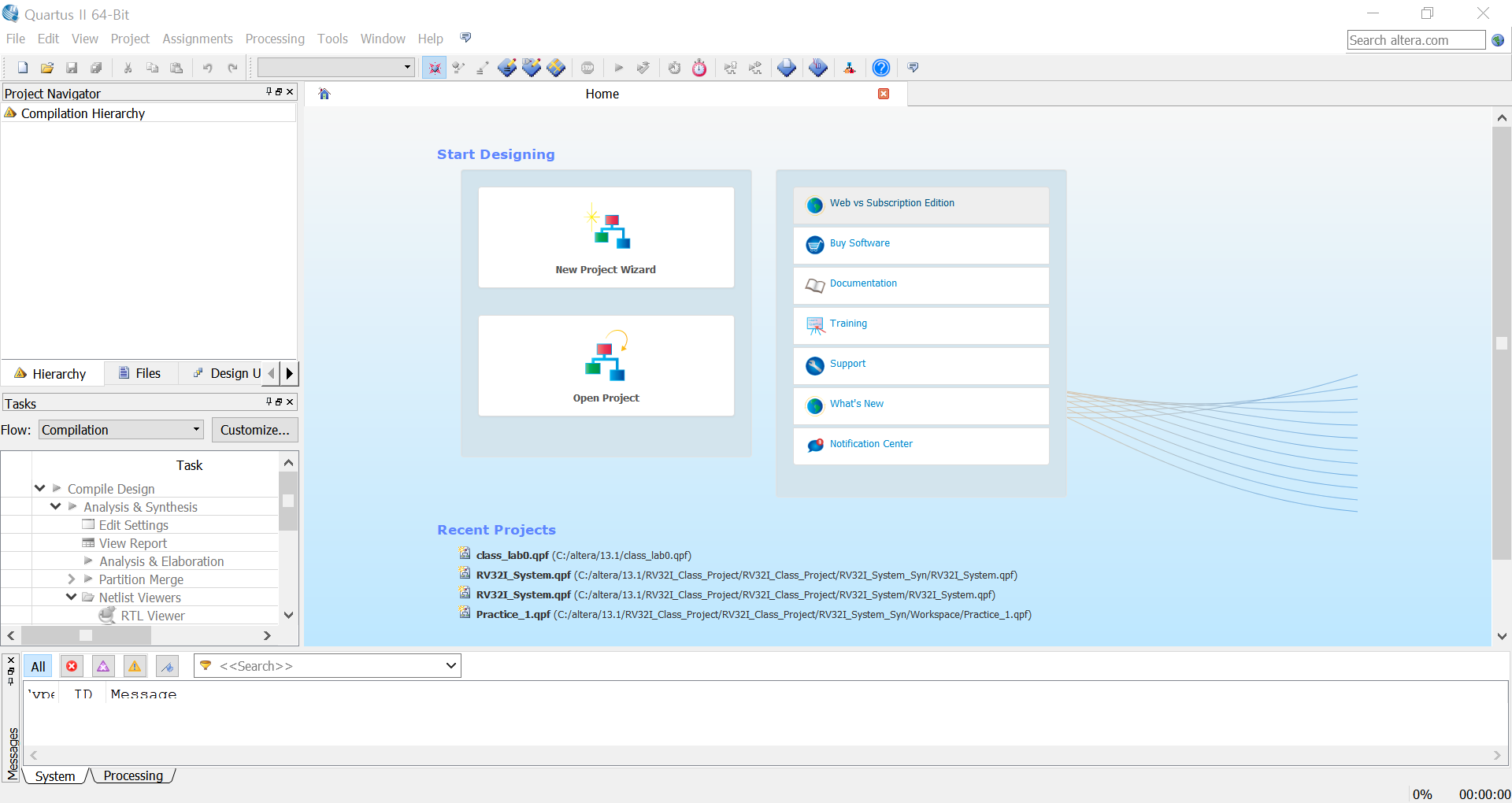

1. 처음 실행시키면 기본 화면이 뜬다.

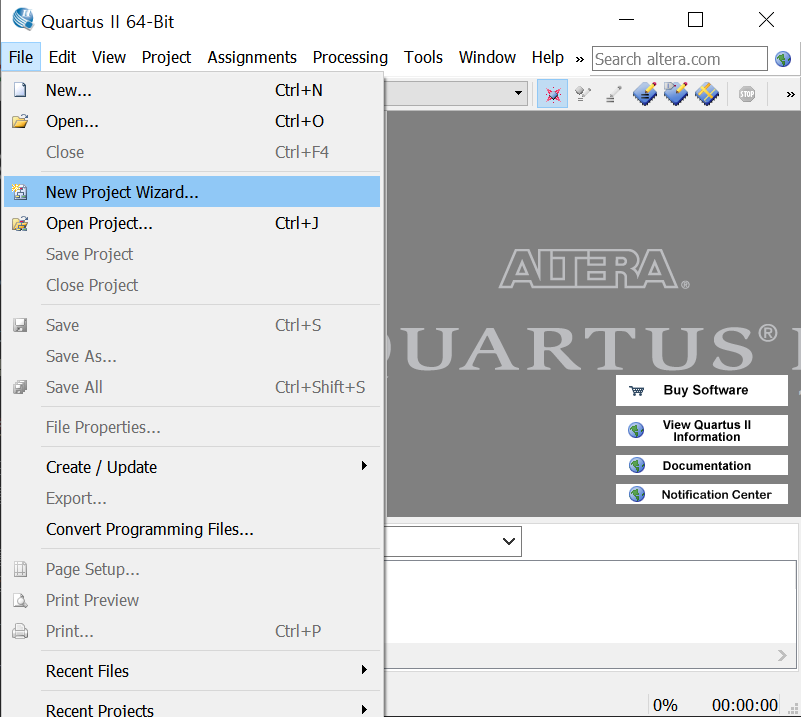

2. 여기서 File을 선택해서 New Project Wizard를 선택한다.

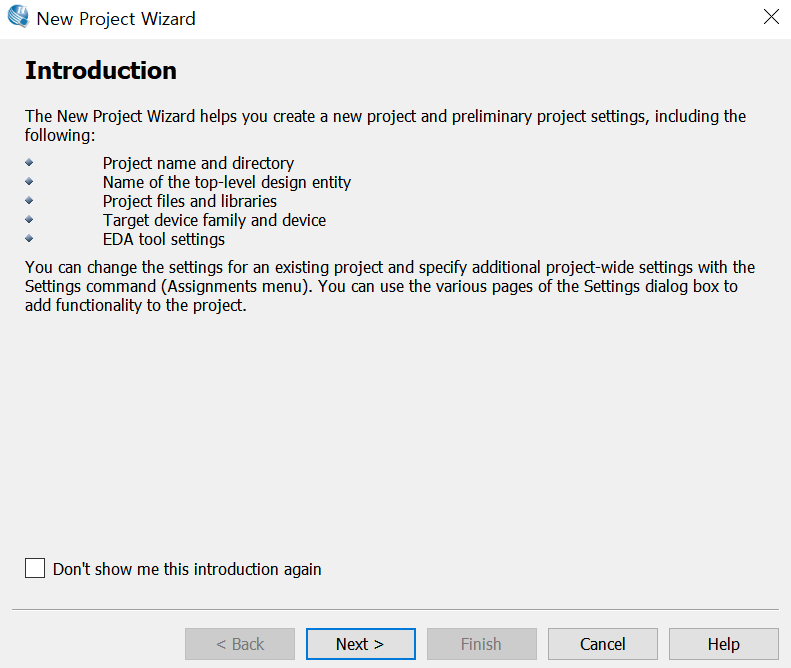

3. 아래와 같은 그림일 뜨는데 Next를 누른다.

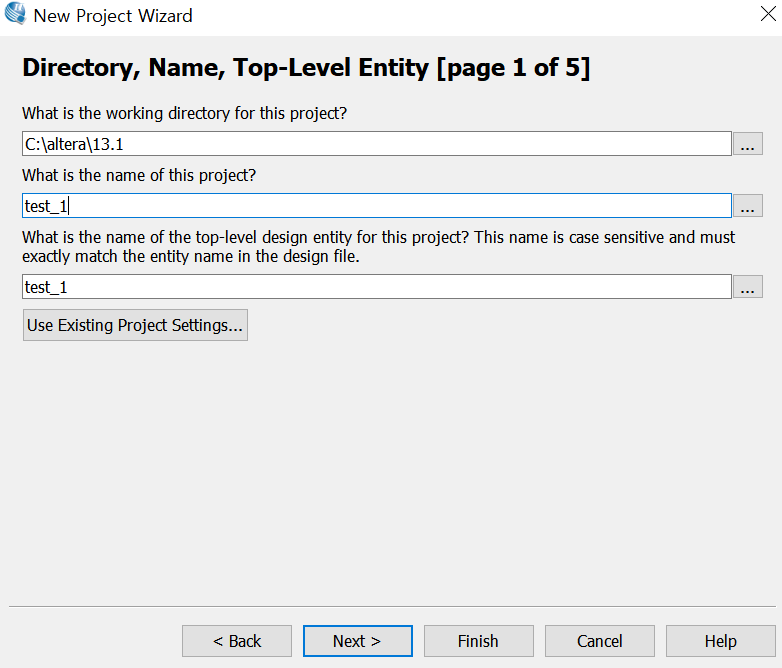

4. 프로젝트명을 적어주는데 이때 top-level 이름과 동일하게 적어줘야한다. 근데 자동으로 동일하게 적힌다.

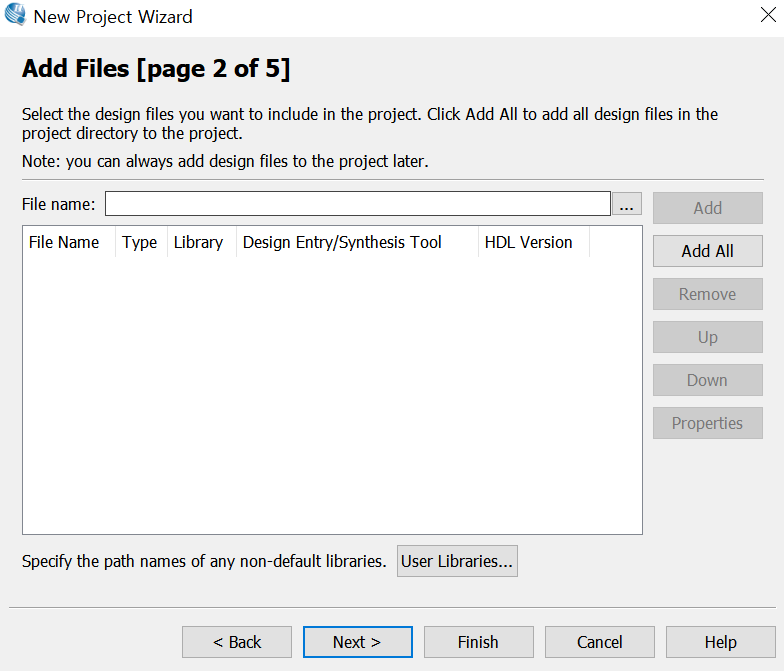

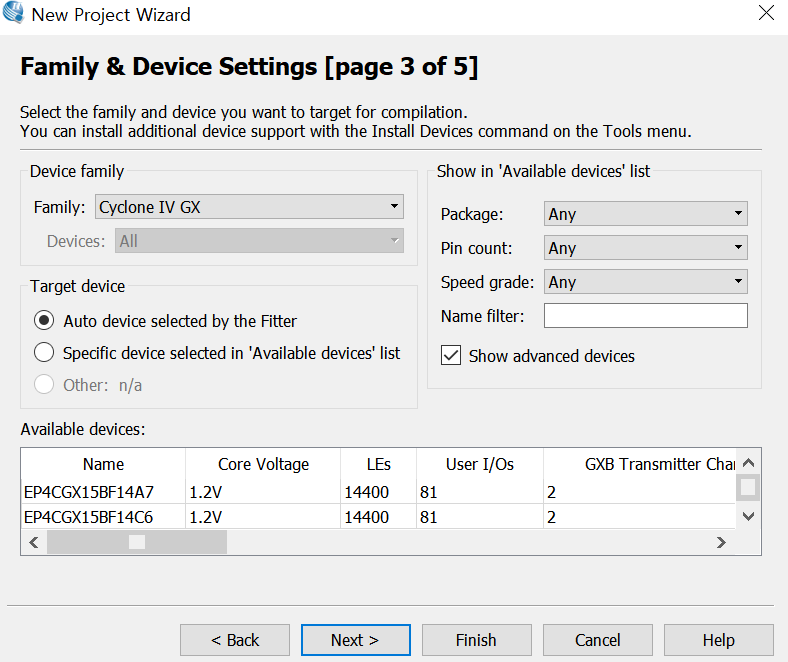

5. 아래 두 화면은 아무것도 안 누르고 Next를 누른다.

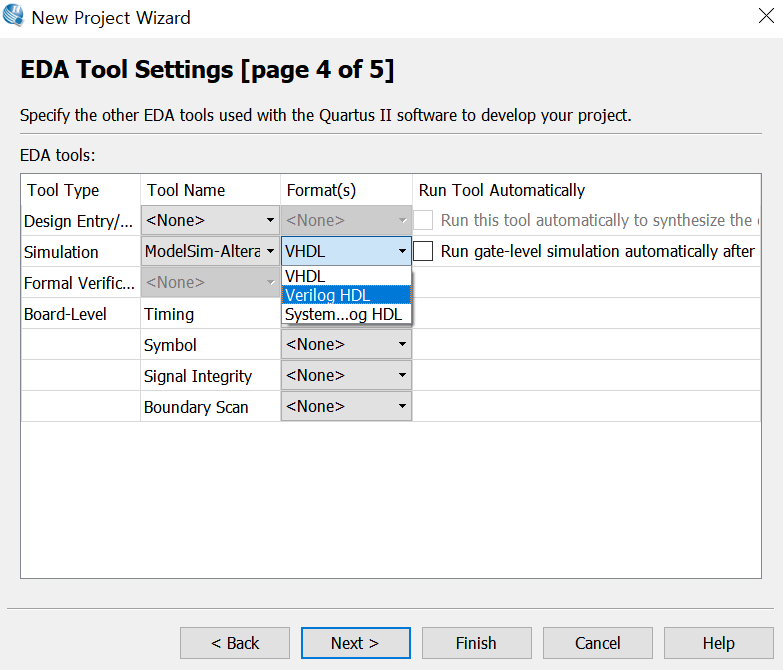

6. Simulation의 Format은 내가 사용할 언어를 지정한다. 본인은 Verliog HDL을 선택했다.

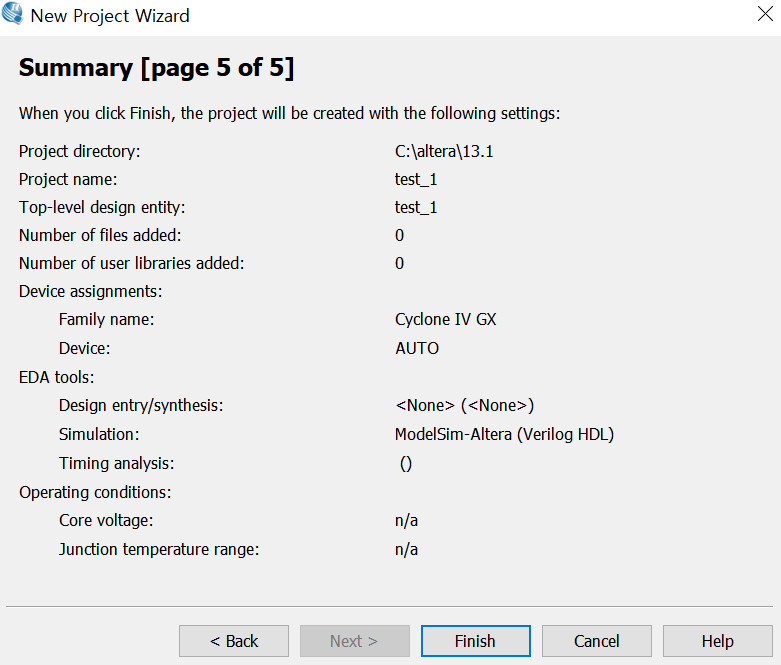

7. Finish를 누르면 내가 적어준 프로젝트가 생성된다.

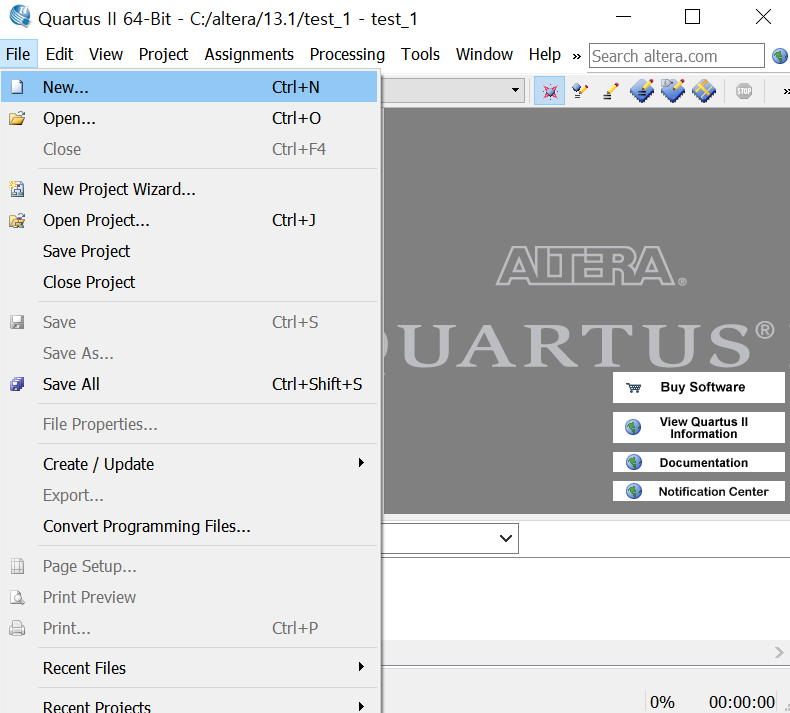

9. 다음으로 내 test_1 프로젝트에서 또 File을 눌러서 이번엔 New를 누른다.

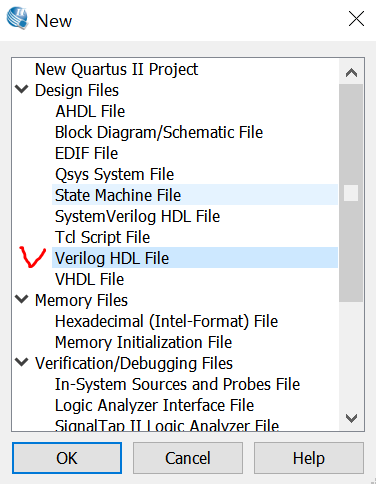

10. 그러면 아래와 같은 창이 뜨는데 이때 어떤 파일을 만들건지 물어보는데 본인은 Verliog HDL을 선택했다.

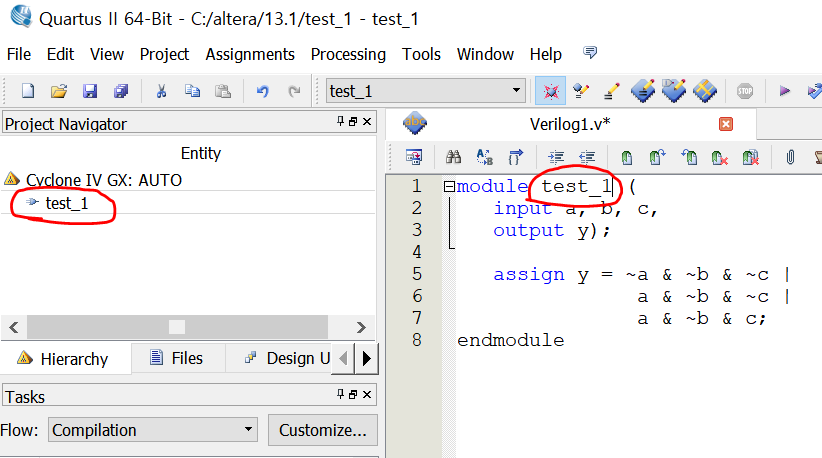

11. 빈 파일이 생성되는데 여기서 간단한 코드를 적었다. 이때 프로젝트명과 module명이 똑같아야 한다.

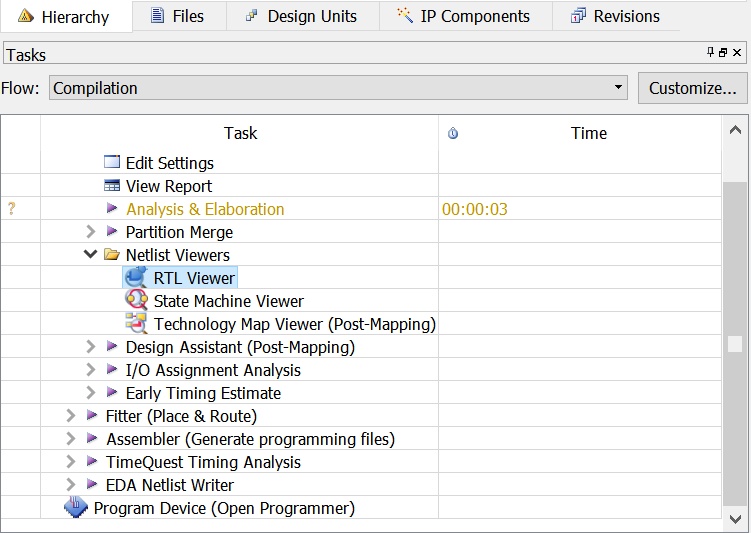

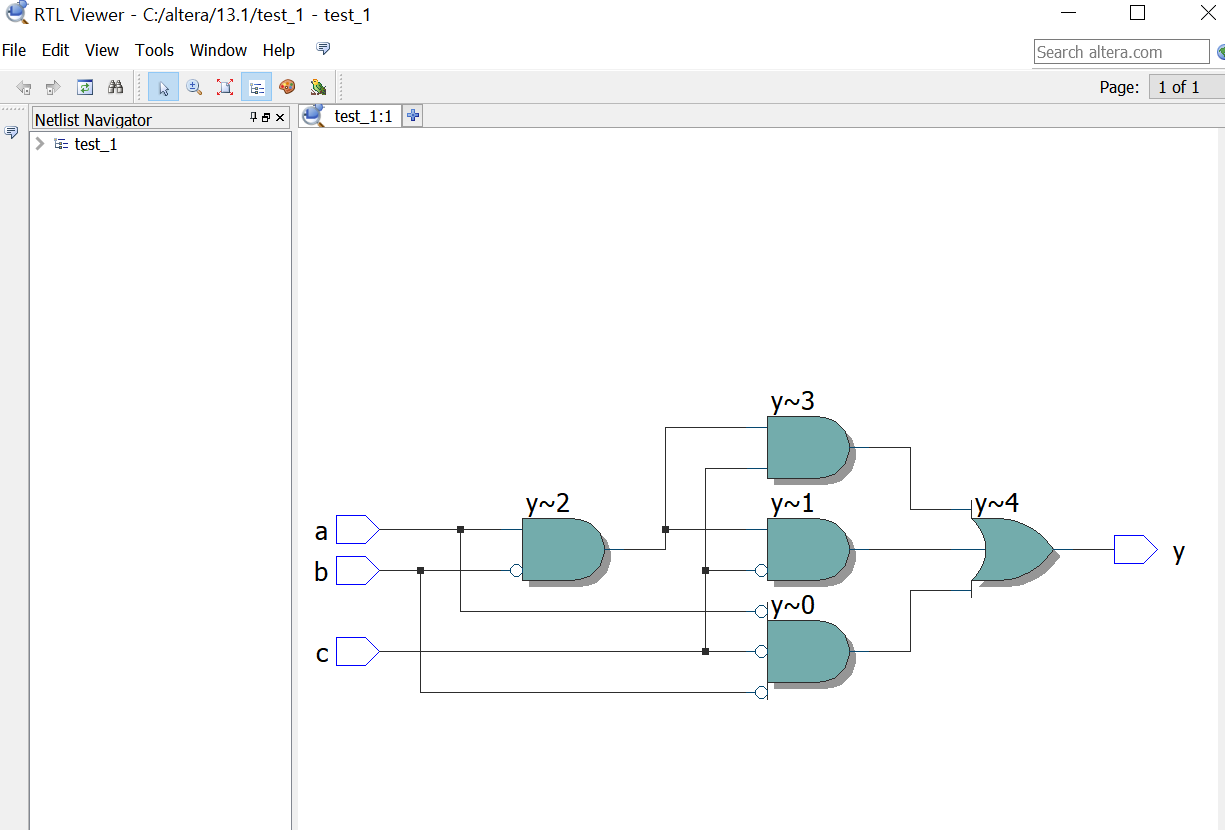

12. 아래 RTL Viewer를 누르면, 내가 짠 코드의 Gate level의 그림을 보여준다.

기존 프로젝트 Open

1. 처음 창은 기본적으로 똑같다.

2. File에서 만들어 놨던 Project를 open하기 위해서 Open Project를 선택한다.

3. 전에 만들어놨던 Quartus 파일이 있다. 이 파일을 선택하면 기존에 만들어놨던 프로젝트를 open 할 수 있다.

반응형

'개발 Tools > Verilog HDL' 카테고리의 다른 글

| Verilog HDL NOR Gate ( Nor 게이트, 4비트 2입력 NOR ) (0) | 2022.02.17 |

|---|---|

| Verilog HDL RCA ( Ripple carry adder, 리플 케리 가산기, 파형, 16bit ) (0) | 2022.02.16 |

| Verilog HDL Multiplexor (멀티플렉서, mux, 예제) (0) | 2022.02.16 |

| Vreilog HDL decoder (디코더) (코드, 예제) (0) | 2022.02.15 |

| Verilog HDL 구문들 ( assign, always, case, initial, 반복문, time scale, self-cheacking test bench, @, 블록문 ) (0) | 2022.02.15 |

댓글