Interrupt (Exception) Handling

SW에서 볼 때는 중간에 어떤 인터럽트가 일어나는지 알 수 없다. 왜냐면 그냥 쭉 실행되는 것처럼 보이기 때문이다. 그렇다면 HW에서 어떻게 동작하는지 알아보자.

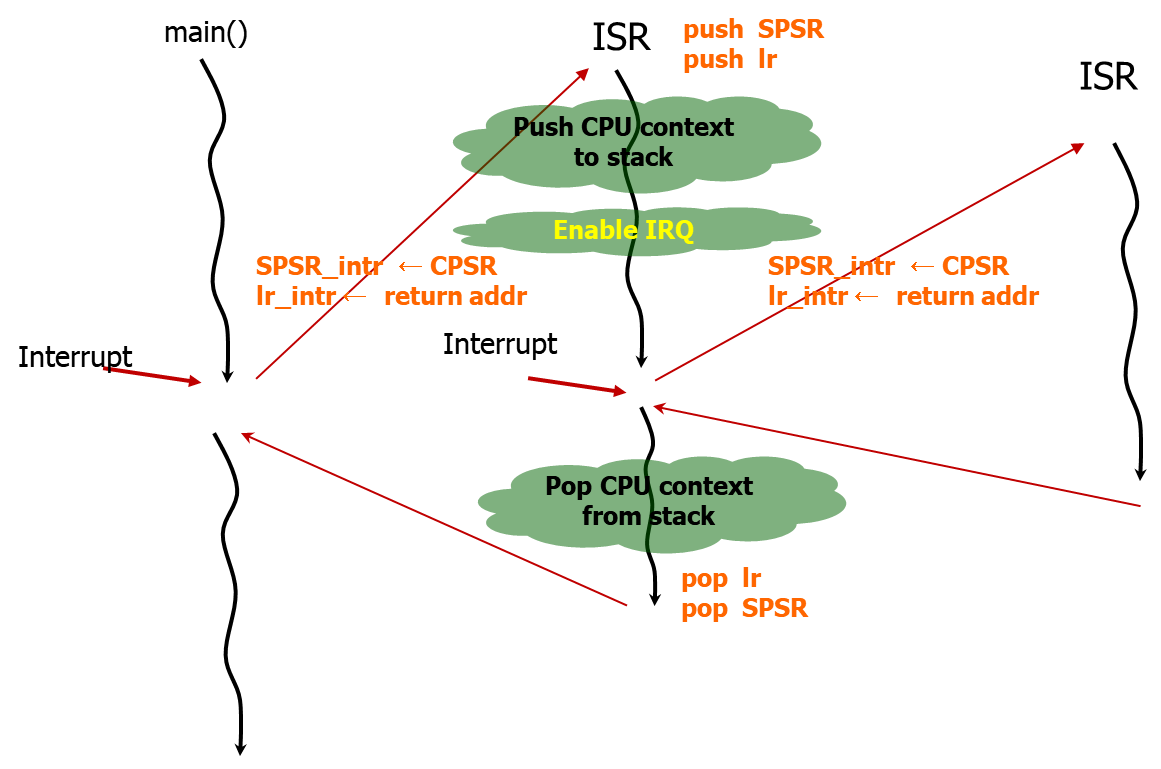

위에 1번에서 일어나는 일은 다음과 같다.

1. exception mode일 때의 CPSR를 SPSR에 저장한다. (CPSR과 SPSR은 같은 구조를 갖기 때문)

2. exception mode일 때의 PC값을 lr( r14 )에 저장한다.

3. CPSR의 mode bitv(i bit or f bit = 1)를 변경하여 해당 exception mode로 변경한다.

( interrupt 처리 중에 다른 interrupt는 받지 않겠다는 의미다. IRQ모드로 바뀌면 i bit가 1로 변경되고 FIQ모드로 바뀌면 i, f bit가 모두 1로 변경돼 된다 )

4. PC에 exception handler table의 해당 주소로 branch 한다.

그다음에는 현재 수행하고 있던 task의 정보를 메모리에 저장해야 된다. 즉, stack에 사용하고 있던 레지스터들과 리턴 주소를 저장한다 ( PUSH ). 정보란 간단히 말해 PCB (= TCB)를 저장하는 것이다.

그리고는 다시 interrupt를 받을 수 있게 interrupt bit를 enable 한다.

위에 3번에서 일어나는 일은 다음과 같다.

1. 저장해 놨던 SPSR의 정보를 다시 CPSR에 저장한다.

2. 저장해 놨던 lr의 값을 PC값으로 바꾼다.

(movs pc, lr or subs pc, lr, #4 )

Nested Interrupt

Nested Interrupt는 ISR을 동작중에 또 다른 ISR이 호출됐을 때를 말한다.

이럴 때는 업데이트했던 lr과 SPSR을 메모리(stack)에 저장하고, 새로 호출된 ISR에 필요한 PC값과 CPSR을 덮어써야 한다.

그러면 SPSR과 lr을 메모리에 push 하고 다 끝나면 pop 해야 한다.

SPSR과 lr을 메모리(stack)에 옮기려면 각각 2번의 명령어를 사용해야 하지만, Arm에선 하나의 명령어로 2개의 동작을 지원해준다.

push : SPSFD (save return status full descending) sp!, #Set_mode

pop : RFEFD (return form exception) sp!

'시스템 반도체 > Arm' 카테고리의 다른 글

| Arm TrustZone ( 신뢰공간, TEE, monitor, banked register, memory ) (0) | 2022.06.24 |

|---|---|

| Arm GIC, SGI ( interrupt controller, 인터럽트 컨트롤러 ) (0) | 2022.05.31 |

| Arm Interrupt Vectors Tables (인터럽트 벡터 테이블, IVT) (0) | 2022.05.31 |

| Arm Interrupt & Exception ( 인터럽트, 예외, 차이점 ) (0) | 2022.05.31 |

| Arm Thumb ( blx, bx, Thumb2, IT명령어, if then ) (0) | 2022.04.26 |

댓글